Part Number: TCA9548A

Dear TI team,

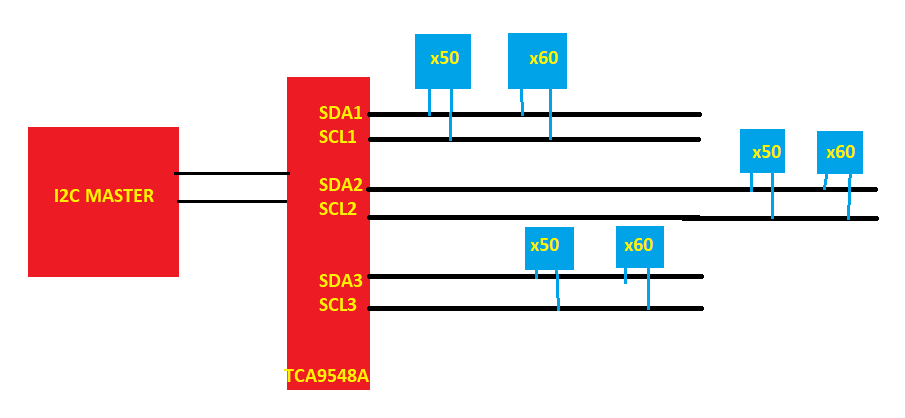

I am interested in using TCA9548A to implement a I2C network as follows:

As you can see, we have i2C devices with the same address. I think it is possible to address I2C devices with the same address through the TCA9548A switch.

As far as I understand the address is composed of the mux (TCA9548) address + the channel address:

But I don´t understand how finally the I2C device is reached. Where is added the address information of the I2C slave device? How the I2C master is able to address the I2C slave device when several devices are connected to the same channel?