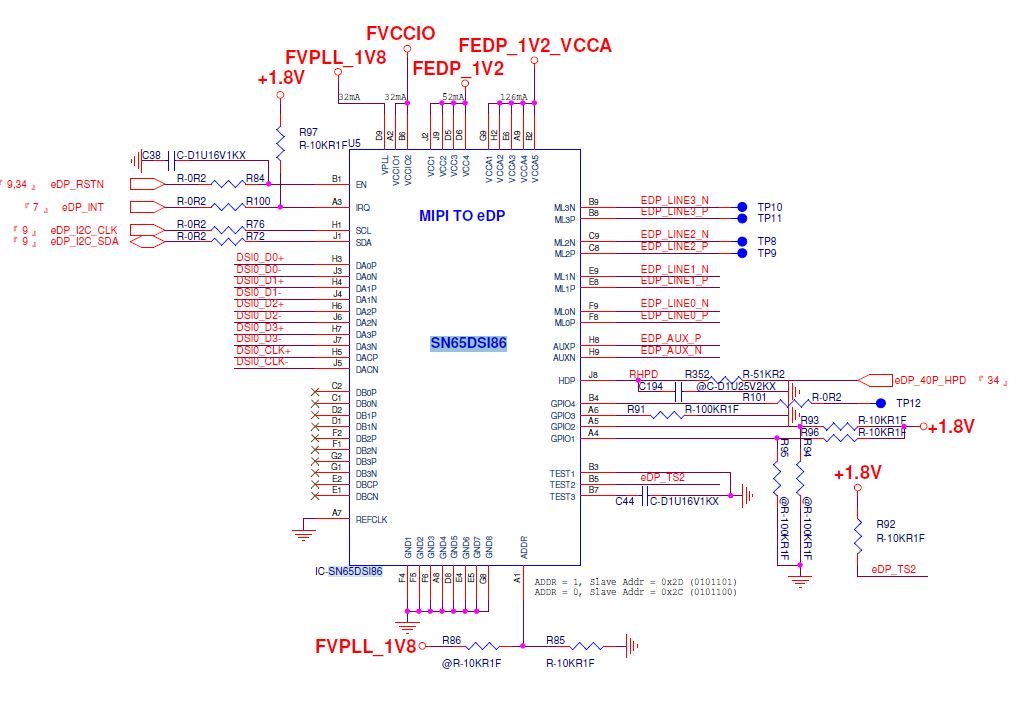

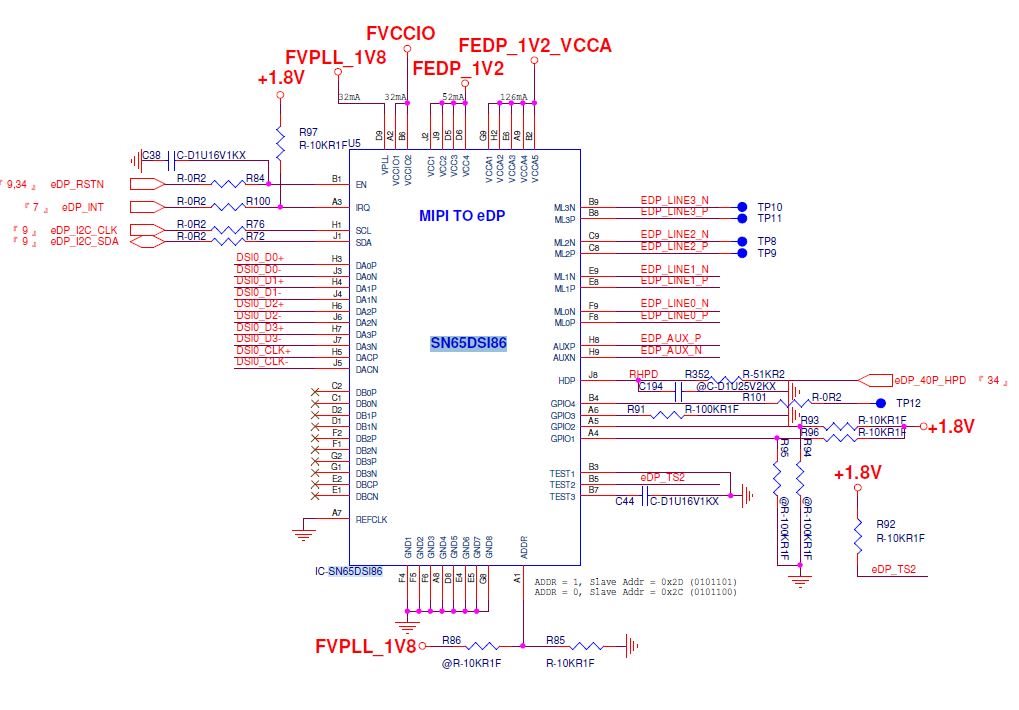

Part Number: SN65DSI86

Other Parts Discussed in Thread: TEST2

Hi

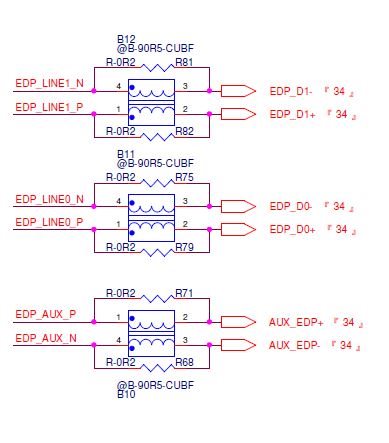

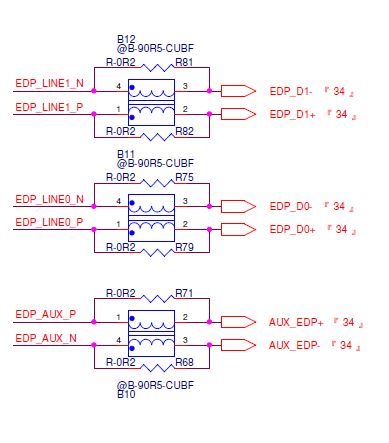

We have SN65DSI86 on Qualcomm SDM450 platform, and try to enable AUO B140XTN02.E but fail.

Have search support forum and try all of suggestion that found here, but still no luck.

Our enable process are:

regmap_write(pdata->regmap, 0xFF, 0x07); // switch to Page 7

regmap_write(pdata->regmap, 0x16, 0x01); // set ASSR_CONTROL writable

regmap_write(pdata->regmap, 0xFF, 0x00); // switch to Page 0

regmap_write(pdata->regmap, 0x0A, 0x03); // REFCLK_FREQ, 384 MHz

regmap_write(pdata->regmap, 0x10, 0x26); // CHA + 4 Lanes

regmap_write(pdata->regmap, 0x5C, 0x01); // disable HPD input

regmap_write(pdata->regmap, 0x12, 0x4C); // CHA DSI CLK Range: 384 MHz

regmap_write(pdata->regmap, 0x94, 0x80); // 2.7 Gbps HBR, Swing Level 0

regmap_write(pdata->regmap, 0x0D, 0x01); // PLL Enable

// check DP_PLL_LOCK succeed

/* 0x64~0x73 AUX_WDATA0 through AUX_WDATA15 => Disable ASSR mode */

regmap_write(pdata->regmap, 0x74, 0x00); //AUX_ADDR[19:16]

regmap_write(pdata->regmap, 0x75, 0x01); //AUX_ADDR[15:8]

regmap_write(pdata->regmap, 0x76, 0x0A); //AUX_ADDR[7:0]

regmap_write(pdata->regmap, 0x77, 0x01); //AUX_LENGTH

regmap_write(pdata->regmap, 0x78, 0x81); //AUX_CMD

mdelay(10);

regmap_write(pdata->regmap, 0x93, 0x24); // 2 DP Lanes

regmap_write(pdata->regmap, 0x96, 0x0A); // Start Semi-Auto Link Training

// check 0x96 ML_TX_MODE_REG

but we always can't not pass Semi-Auto link, the status always indicate main link off.

The error registry dump show as below

sn65dsi86_dump_err_reg()

0xF0h = 0x00

0xF1h = 0x00

0xF2h = 0x00

0xF3h = 0x00

0xF4h = 0x08

0xF5h = 0x00

0xF6h = 0x00

0xF7h = 0x00

0xF8h = 0x02

We have try:

1. force force ML_TX normal, but no data display on screen.

2. try others training mode TPS1, TPS2, and etc, but only fast link can pass, but still no data display on screen.

3. adjust VOD level, swing level, but still no pas training.

4. using PANEL_VIDEOREGISTER_CALC.xlsm to fill up EDID data from panel datasheet, but still not help.

5. ignore training, just enable color bar test pattern, but no data display on screen.

Have any suggestion that we can try? Thanks.

Rick