Other Parts Discussed in Thread: DS90UB953-Q1EVM, ALP

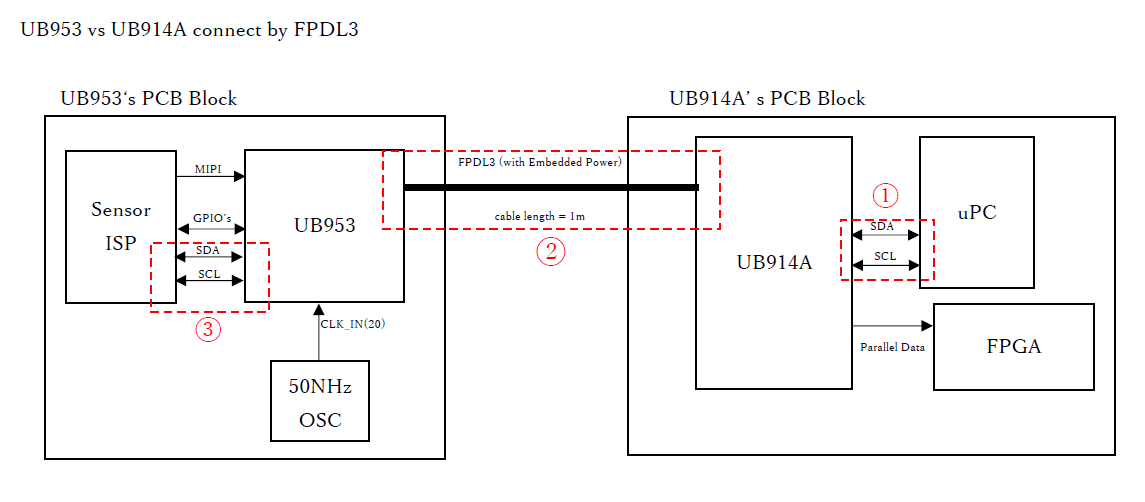

We can't I2C communication with S90UB953-Q1 and DS90UB914A-Q1.

Master device is my I2C host controller.

[a:sensor] <I2C > [b:953] <I2C> [c:914] <I2C> [d:I2C Host Controller]

slave address

a:sensor = 0x42

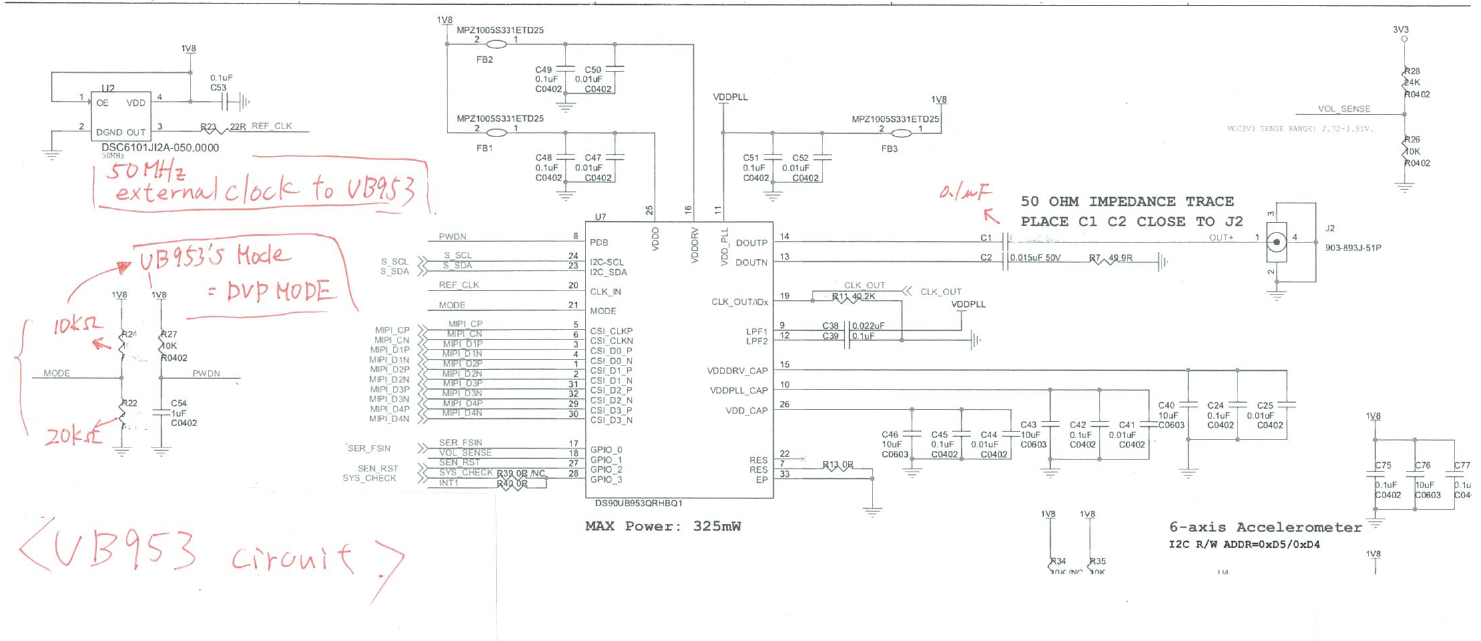

b:953 = 0x30 (maybe I thnk 0x30 is default slave address??)

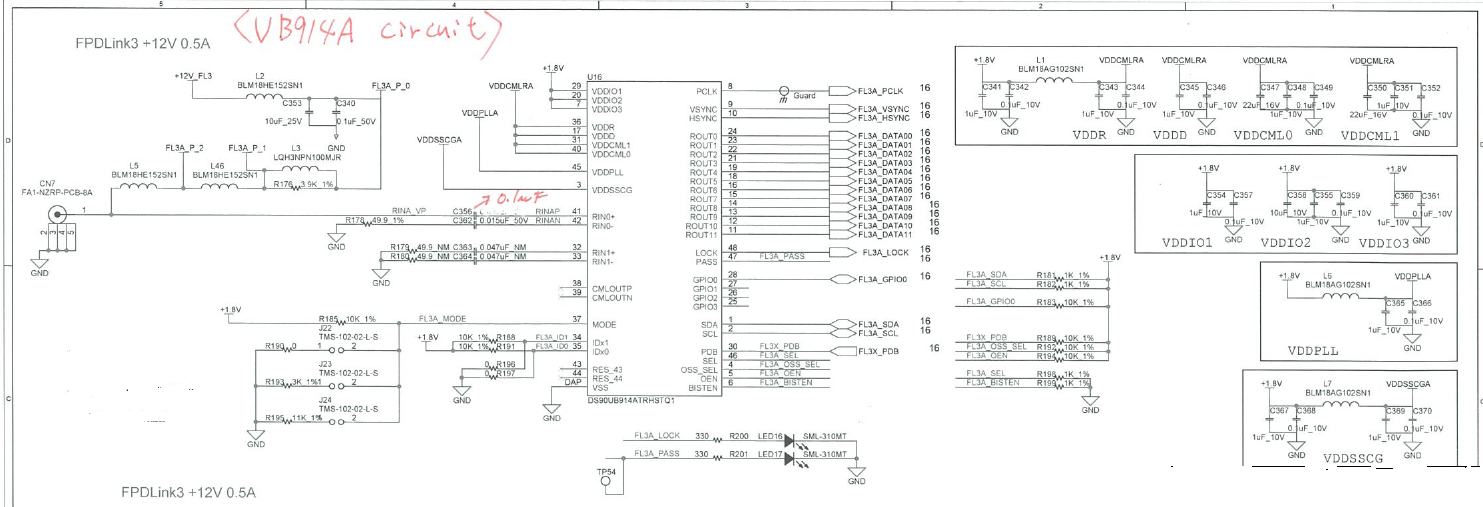

c:914 = 0x60

We tried following steps.

step1) The 953 MODE pin setted DVP. So serdes signal linked 953 and 914.

step2) I2C access [d:I2C Host Controller] and [c:914].

Access was suceeded. So set some parameters for accessing [b:953].

setting 914's registers

@write address 0x06 to 0x30(953 I2C slave address)

@write address 0x07 to 0x30

@write address 0x08 to 0x42

@write address 0x09 to 0x42

First of all, I would like to access the 914 to 953 registers via I2C.

Please tell us what we should check.

Best regards.