Hi there,

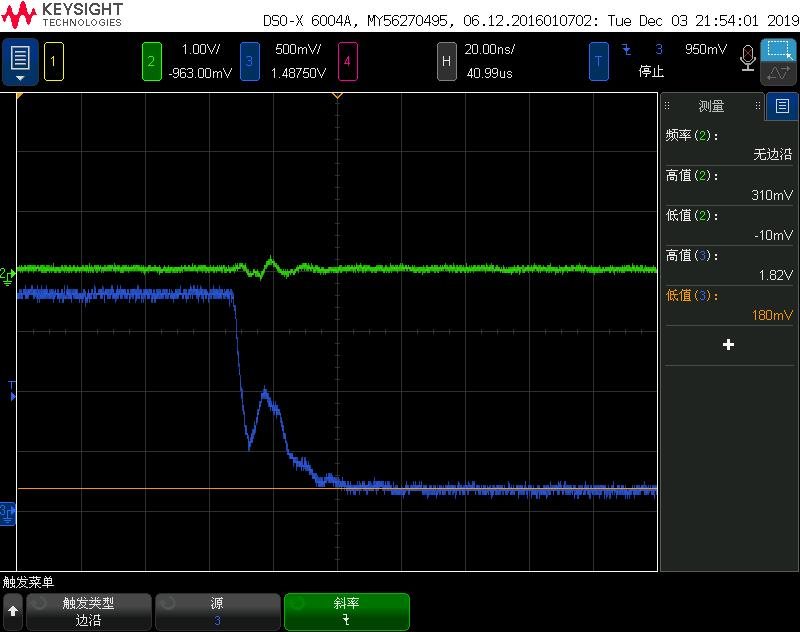

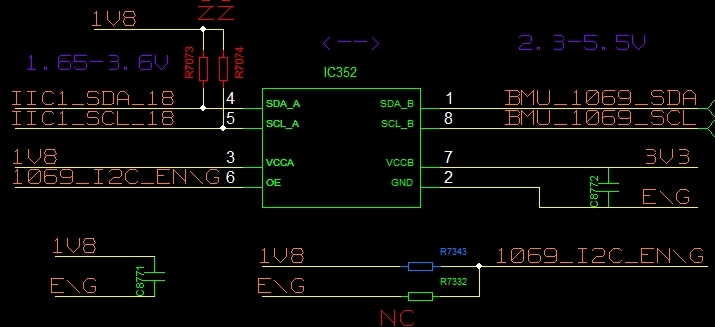

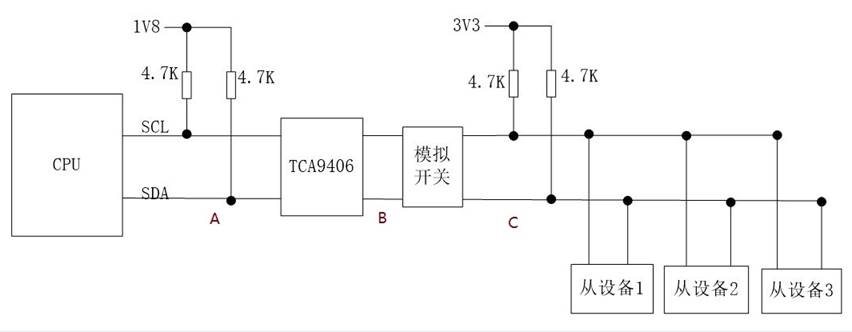

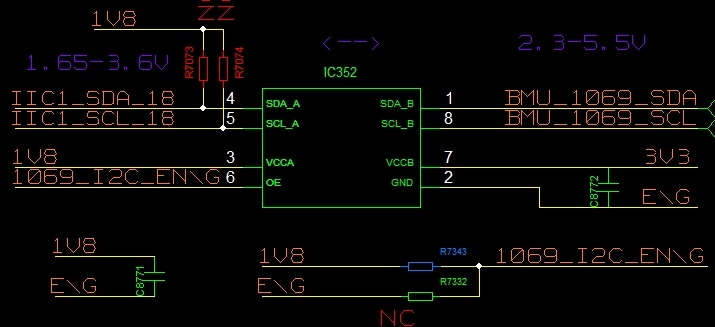

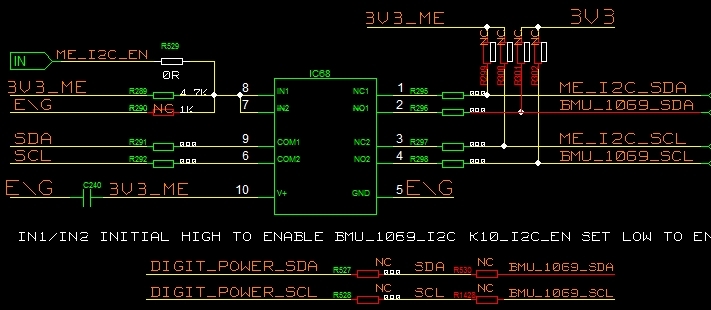

My customer found the falling edge of SDA_A and SCL_A is not monotonically decreasing. The glitch may trigger data error of I2C communication. After disconnect SDA_A and SCL_A from I2C bus, the glitch disappears. Customer replaced TCA9406 with TCA9417, and it doesn't have the same issue.

My question is how to eliminate the glitch of TCA9406.

Thanks.