Dear support team;

I have 2 questions.

1) PLL Lock Time

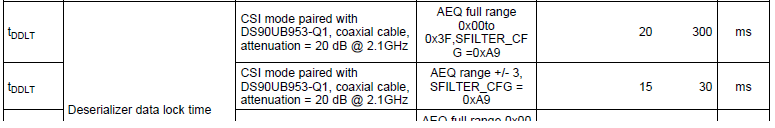

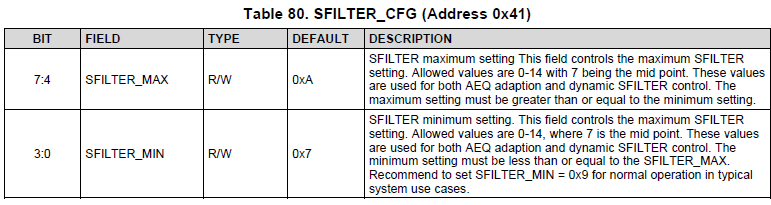

On datasheet, PLL lock time is defined the following time with DS90UB954-Q1.

But, I think that this value is not default register setting.

Could you tell me the maximum and typical lock time when using default register value?

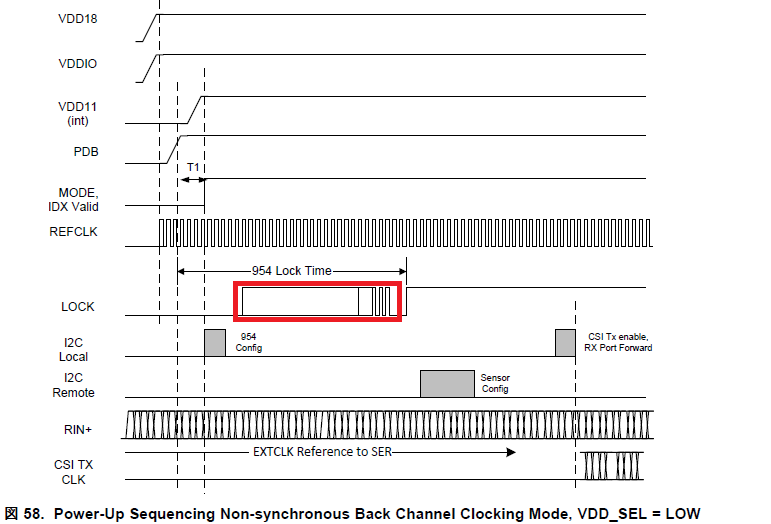

2) Lock signal

I think that LOCK signal is Lo continuously while the following red term.

Or LOCK signal is unstable(Hi and Lo)?

Because, I would like to check the LOCK status by using MCU interrupt via LOCK signal.

How do you think?

B.R

Masaaki Sugiyama