Part Number: DS160PR410

Hi

We use the DS160PR410 for PCIe Gen 4 AIC

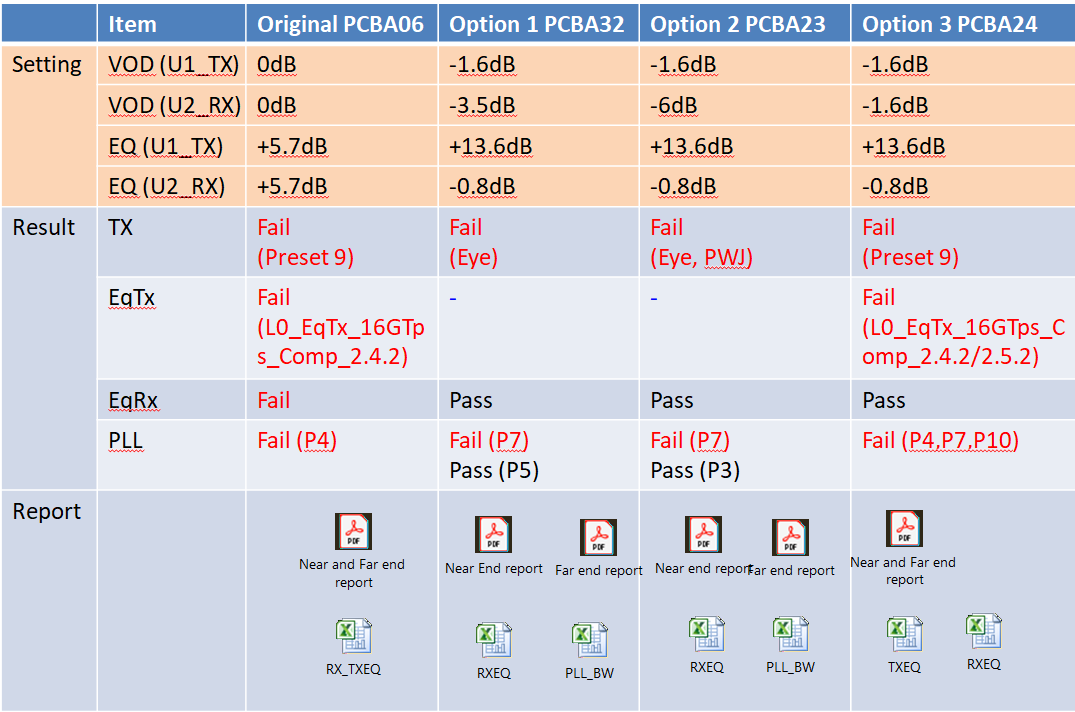

I have test with the TX compliance test, and PLL_BW test

For PLL_BW

I try to set CTLE to index 0 can Pass the PLL_BW, and Index 1 and over will be fail

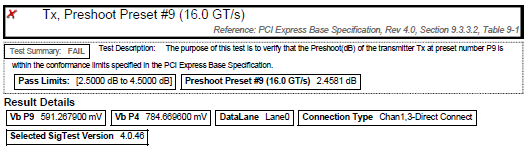

For TX compliance

I try to set VOD to Index 0 1 2 3

Index 2 and 3 will fail TX Preshoot Preset #9

Index 0 and 1 will Pass TX Preshoot Preset #9 issue, but our far end eye will fail

Could provide the DS160PR410 CTLE and VOD adjustment suggest for me?

Let me can Pass the TX compliance.