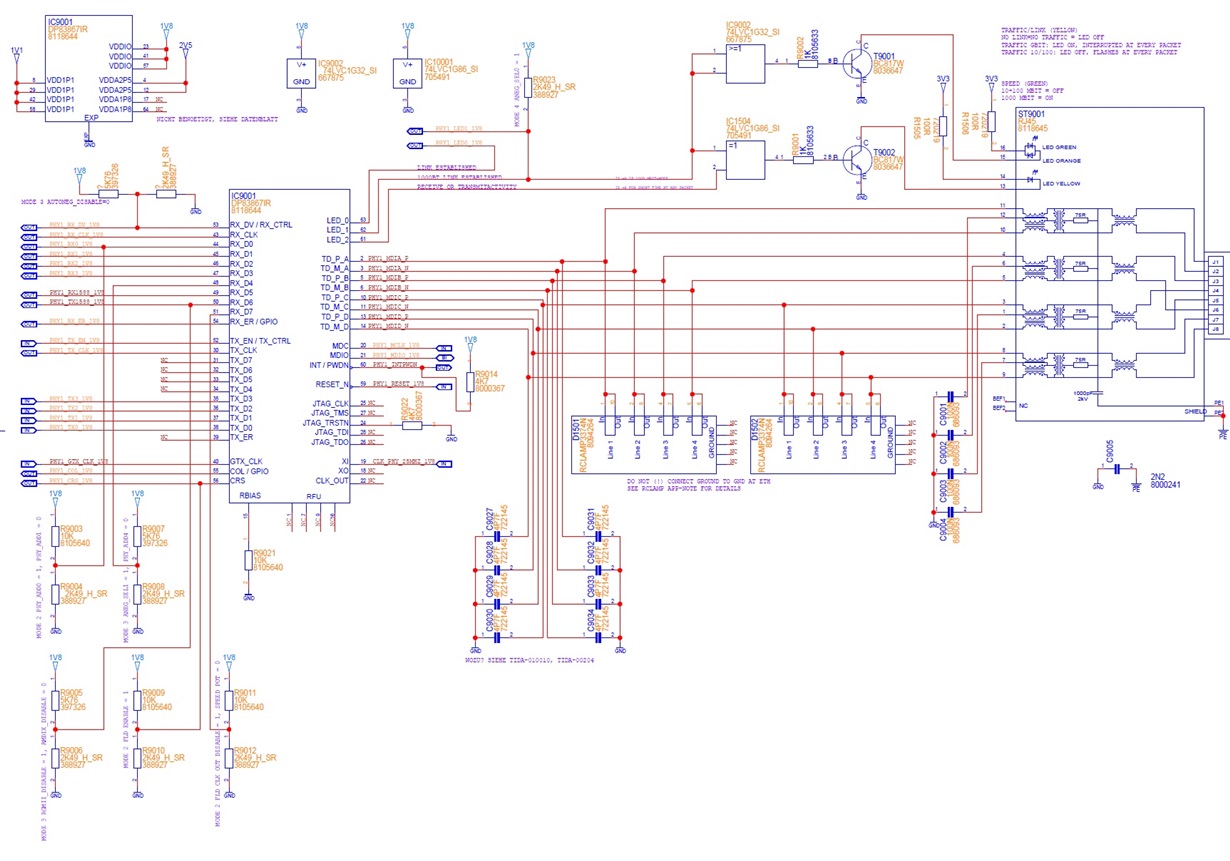

Part Number: DP83867IR

Hello,

I am trying to connect the DP83867 to an FPGA design via MII only. For this specific design, no GMII or RGMII interface is available.

The PHY is configured for 100/10 MBit only and is connected to a 1GBit switch. After auto-negotiation, the PHY selects a 100MBit connection and RX_CLK is clocked at 25MHz. My problem now is, that TX_CLK stays low all the time.

How can I check if the PHY is actually in MII mode? How can I "force" MII mode and under which conditions the PHY is enabling TX_CLK?

After reading the datasheet for multiple times, I am still not 100% sure if I should actually enable or disable RGMII to get MII mode for 100/10 Mbit connections.

What does the line "The MAC holds the RGMII TX_CLK low until it has ensured that it is operating at the same speed as the PHY" actually mean? Another forum post suggests that this refers to TX_CTRL instead of TX_CLK. Do I have to pull TX_CTRL high to enable TX_CLK?

Thank you very much in advance!

Kind regards

Stefan