Hi Team,

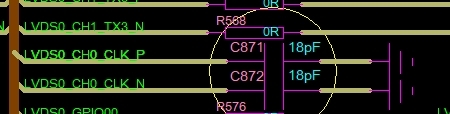

As we know, sometimes in order to improve EMI performance, consider adding a small capacitor at both ends of CLK +/- like the below picture, which will also slow down the clock's raise time and fall time.

So I want to confirm what are the requirements for the raise time and fall time of 947? Or how to determine the value of this capacitor? Thanks.

Best regards,

Ansel