Other Parts Discussed in Thread: DP83867ERGZ-R-EVM

Hello,

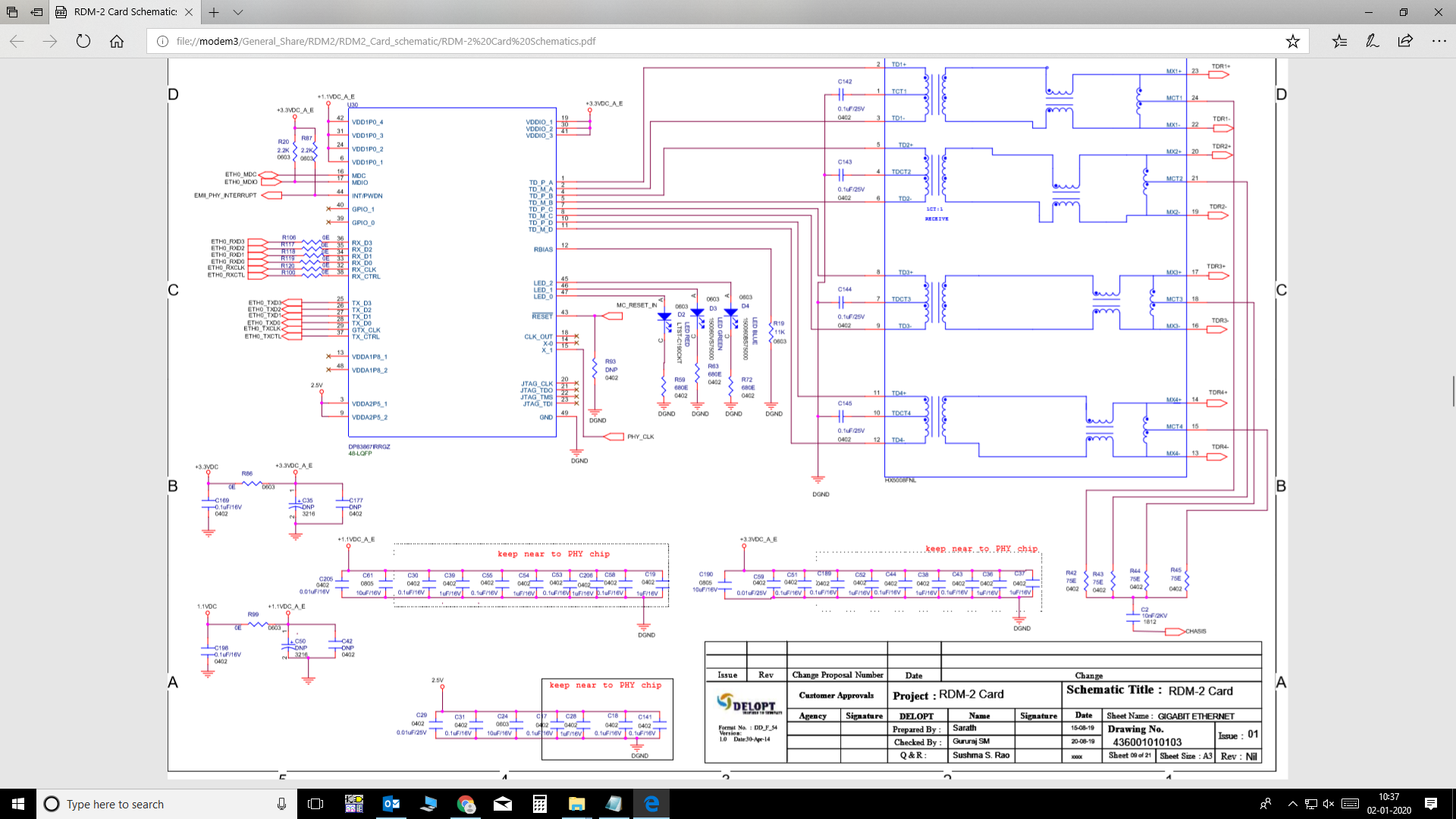

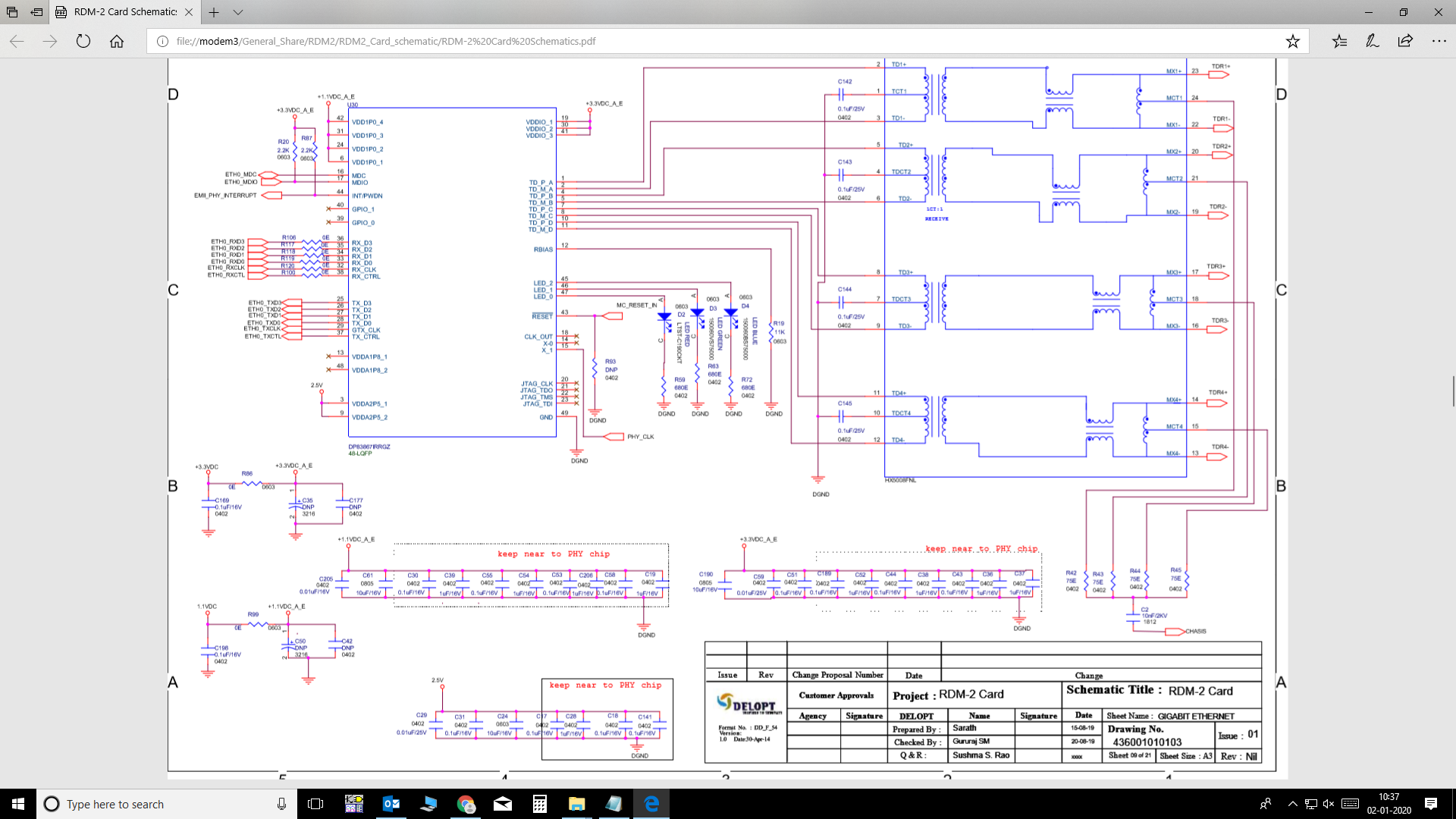

We are using gigabit phy Ethernet in RGMII mode it was working fine in my PC (LINUX RHEL 7.3 OS) but when i connect the gigabit switch between my card and PC i cannot able ping the card and by debugging i came know that it had struck in the interrupt and it was not coming out from that until switch is Disconnected is there related to hardware or software by the way we have followed the same from DP83867 EVM schematics please help me to come out from the issue

Regards

Sarath M