Part Number: TPS65987D

Other Parts Discussed in Thread: TPS65987, TIDA-050012

Hello,

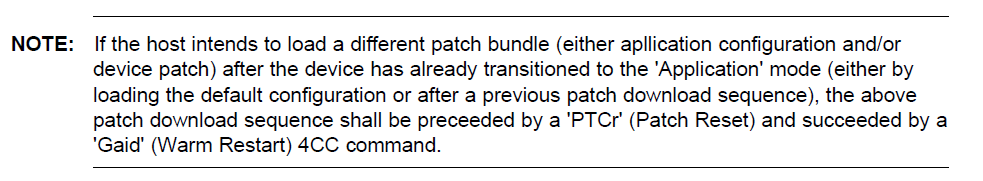

I'm attempting to update a TPS65987D over I2C following the PTCx command sequence.

I successfully transfer all the data in chunks of 64 bytes, but upon sending the PTCc command, in Byte 3 of the response, DevicePatchCompleteStatus I receive a 0x42 (Patch not compatible with this version of ROM).

My device is a TPS65987DDHRSHR, and the utility I used to get a patch file was version 6.1.1, using the TPS65987_88_F707_10_08.bin

This same patch successfully loads to the EVM from the utility and runs correctly.

I have tried multiple new, and stock patch files with the same 0x42 result.

Attached is a link to my i2c capture of the whole patch update. (External link due to file upload extension rules):

https://drive.google.com/open?id=10JelenN30IFiRcX4KKddaJjvHSRX_6JE

This capture covers going from:

- PTCr

- PTCs

- PTCd (Iterated for whole Patch)

- PTCc (Has the 0x42 error)

The file can be opened using Total Phase Data Center. The error is annotated at the bottom.

This seems to be the same issue as http://e2e.ti.com/support/interface/f/138/t/842397?TPS65987D-TPS65987D which had no resolution.

Any help would be appreciated,

Jeff