Part Number: SN65DSI84

Other Parts Discussed in Thread: DSI-TUNER, SN65DSI85

Hi,

We have designed a new board based on Rockchip RK3399 that has MIPI DSI display interfaces. We are using two SN65DSI84 chips to interface the CPU to two LVDS displays.

We have now struggled getting the bridge to work. Last week we were able to output test pattern although the initialization sequence was not correct. Now when we have fixed the initialization, the PLL_UNLOCK bit is set and it won't clear suggesting a problem with clock. We can't even get the test pattern anymore despite the sequence is now according to specification. However, as the PLL was locking last week with the same board with wrong initialization, we are a bit puzzled.

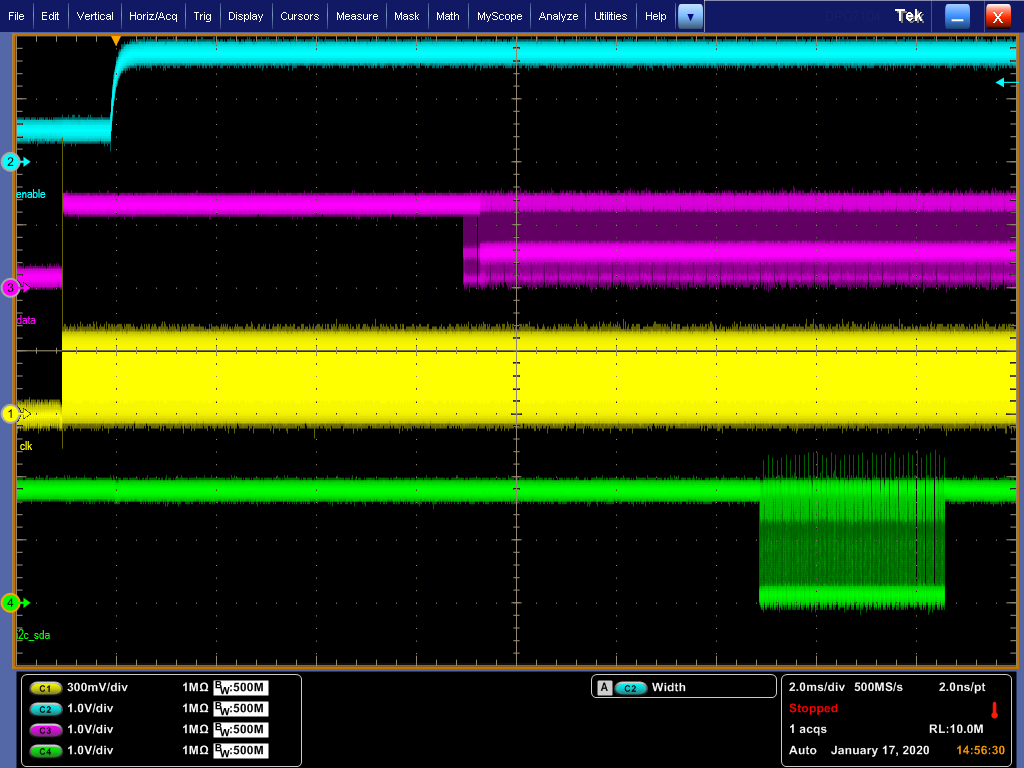

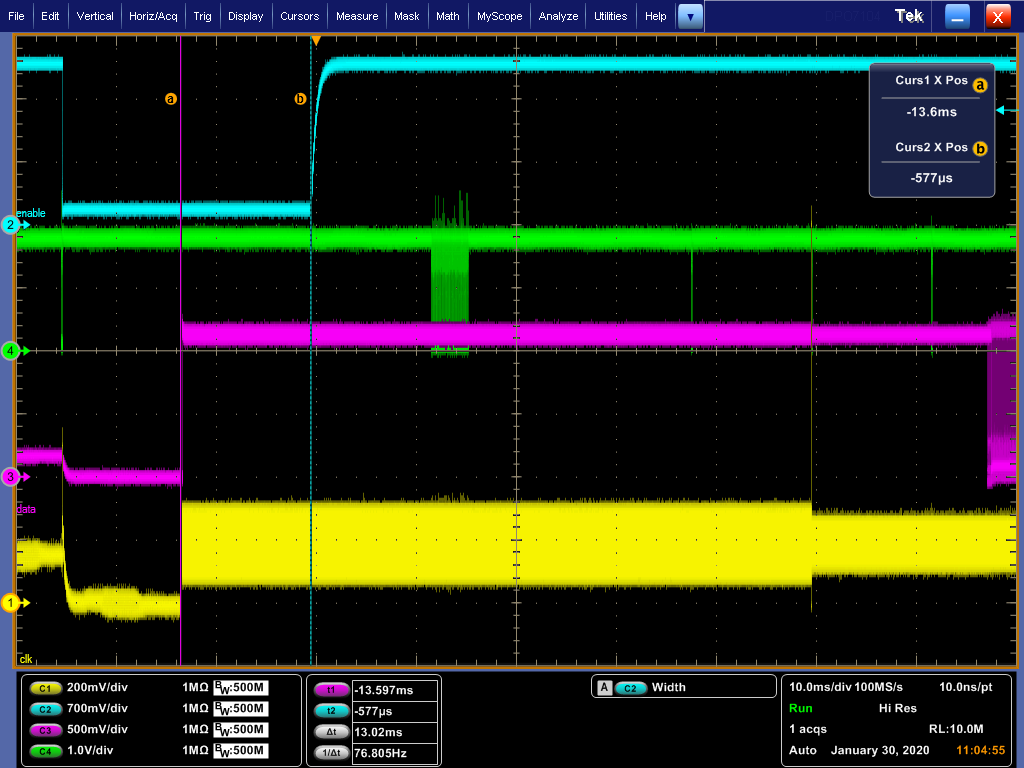

We know that the initialization might cause odd problems, but correct sequence has been confirmed with oscilloscope, see attachment.