Hi Team,

We have met problem in using DS250DF410, detail as follow:

For now, we can lock the CDR but can not receive the date in receiving end.

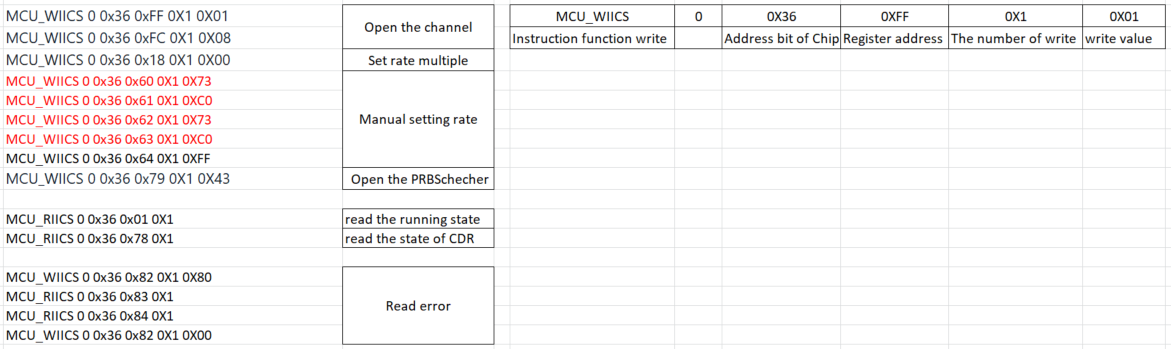

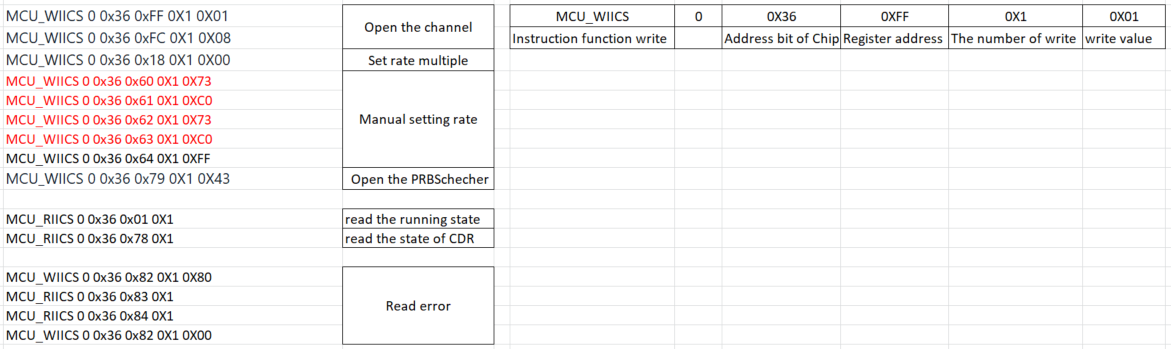

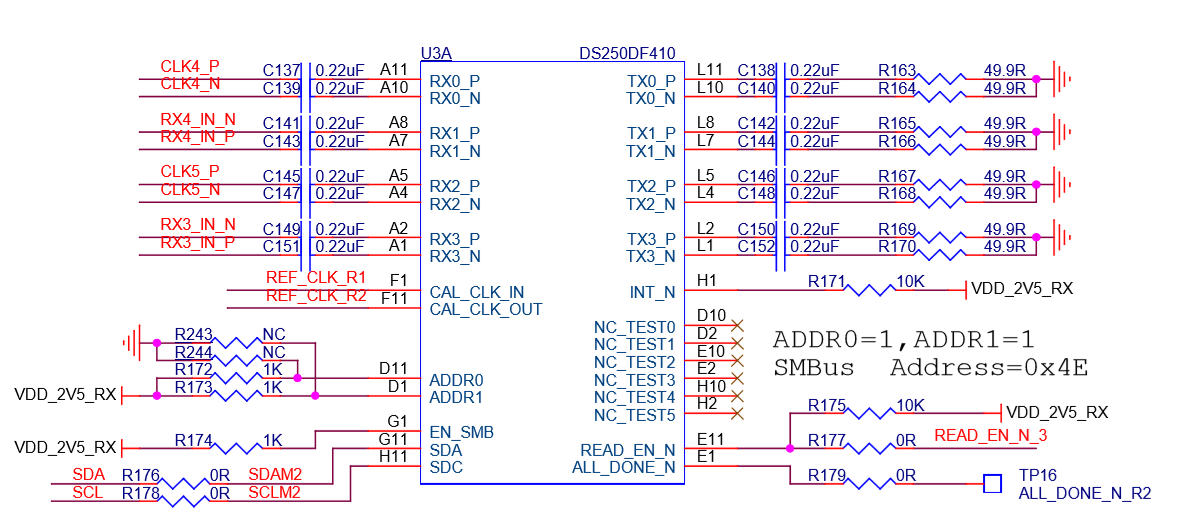

can you give me some suggestions in this case? i upload the schematic and register

Hope you can help me. Thanks a lot.