Part Number: SN65DSI83

Other Parts Discussed in Thread: DSI-TUNER

Hi,

I am currently using the evaluation board of the SN65DSI83.

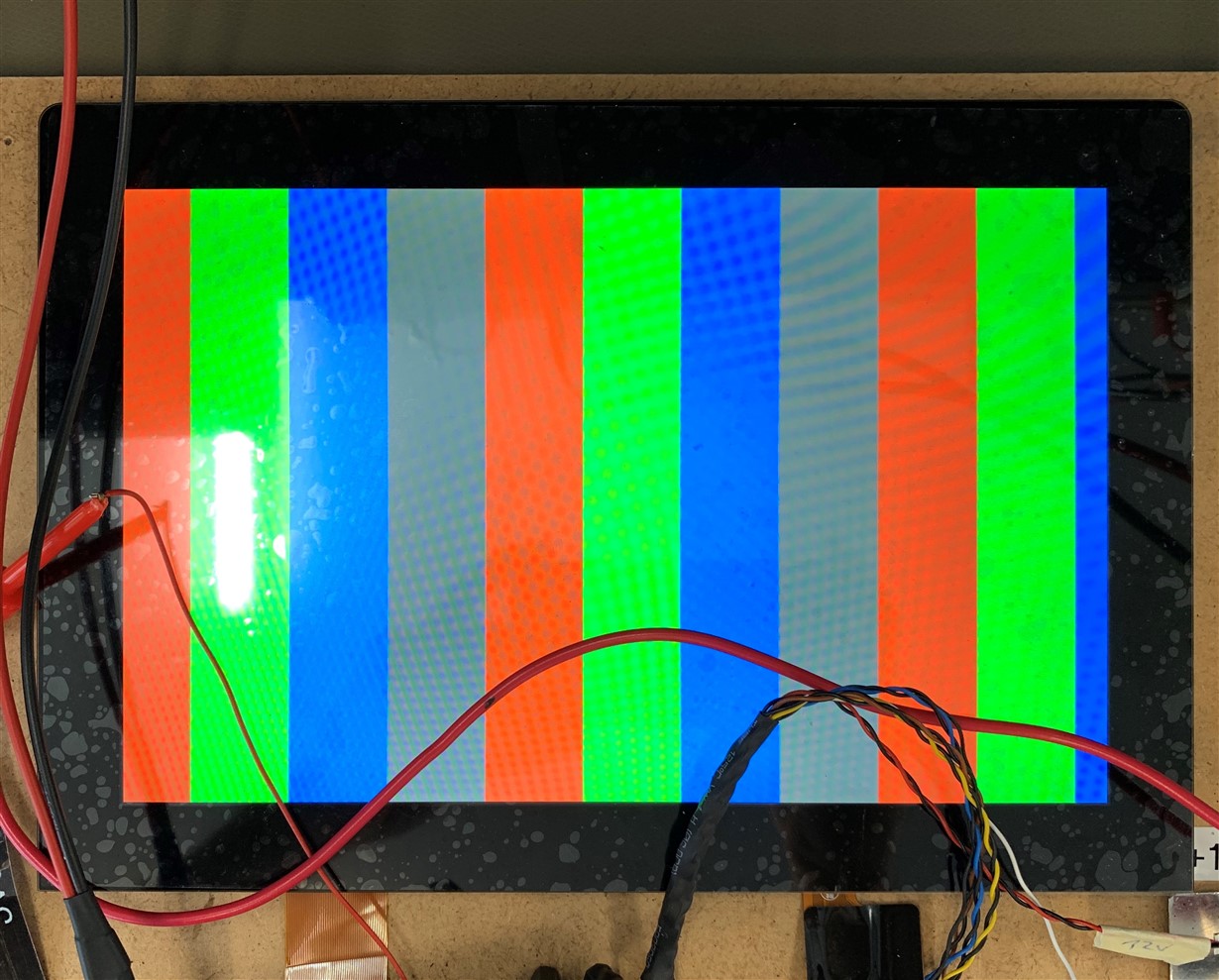

At first I would like to show the test pattern on my display (AUO B101EAN01.2).

I want to use the 27MHz LVDS_RefCLK for the lvds clock.

(from Y1, have checked the frequency at R33)

If I check the LVDS signals at J6 on channel A, I measure the data signals correctly, but I don't measure a signal at FlatChA_CLKP and FlatChA_CLKN.

For the dsi tuner I have selected the following settings.

Would be glad if someone could help me.

Thanks