Part Number: DP83848I

Hi,

I'm having trouble with the DP83848I to establish a link.

-

The communication partner is one factor. I tried different Network Interface Cards and switches: the success of establishing a valid link varies between 5% and 100%.

-

The success rate between specific devices from one production batch also varies strongly.

So I took a closer look at the status registers:

-

BMSR: Basic Mode Status Register

-

PHYSTS: PHY Status Register -

ANLPAR: Auto-Negotiation Link Partner Ability Register -

ANER: Auto-Negotiate Expansion Register

What I found out so far:

-

After plugging in an Ethernet cable, nothing happens with regard to the status registers:

BMSR:0x7849 / PHYSTS:0x0000 / ANLPAR:0x0000 / ANER:0x0004$

BMSR:0x7849 / PHYSTS:0x0000 / ANLPAR:0x0000 / ANER:0x0004$

BMSR:0x7849 / PHYSTS:0x0000 / ANLPAR:0x0000 / ANER:0x0004$

BMSR:0x7849 / PHYSTS:0x0000 / ANLPAR:0x0000 / ANER:0x0004$

-

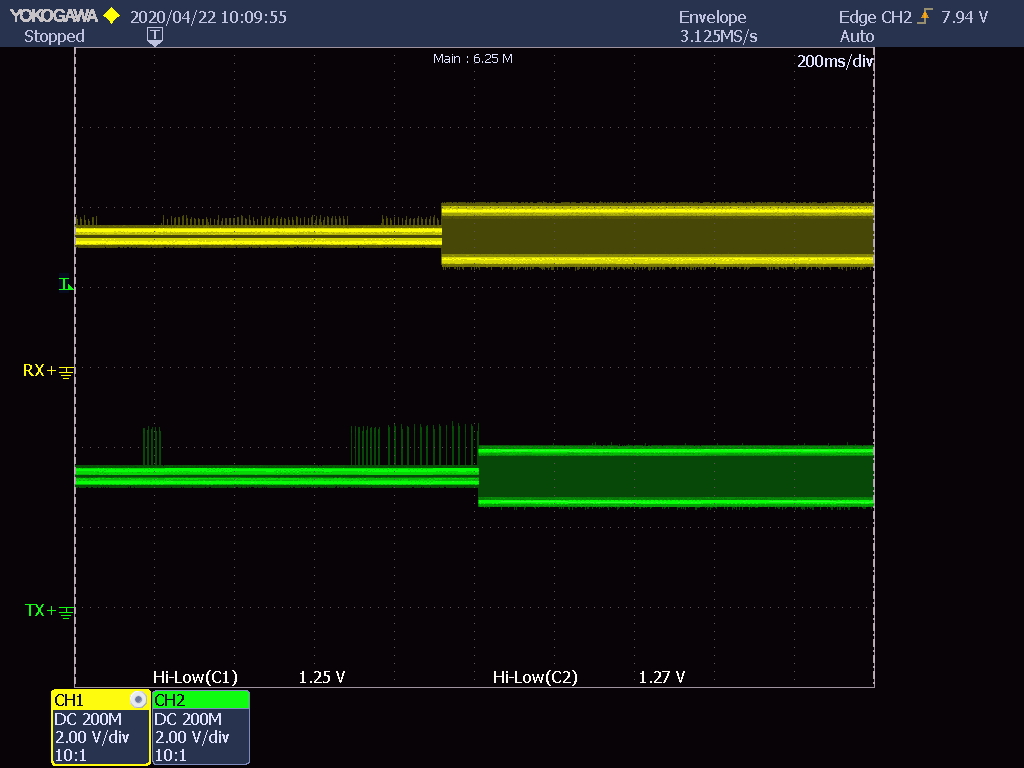

When I pull the plug, the Auto-MDIX functions starts swapping the MDI pairs (

PHYSTS:0x4000means "MDI pairs swapped"):BMSR:0x7849 / PHYSTS:0x0000 / ANLPAR:0x0000 / ANER:0x0004$

BMSR:0x7849 / PHYSTS:0x4000 / ANLPAR:0x0000 / ANER:0x0004$

BMSR:0x7849 / PHYSTS:0x0000 / ANLPAR:0x0000 / ANER:0x0004$

BMSR:0x7849 / PHYSTS:0x0000 / ANLPAR:0x0000 / ANER:0x0004$

BMSR:0x7849 / PHYSTS:0x0000 / ANLPAR:0x0000 / ANER:0x0004$

BMSR:0x7849 / PHYSTS:0x4000 / ANLPAR:0x0000 / ANER:0x0004$

BMSR:0x7849 / PHYSTS:0x0000 / ANLPAR:0x0000 / ANER:0x0004$

BMSR:0x7849 / PHYSTS:0x4000 / ANLPAR:0x0000 / ANER:0x0004$

-

Now if I put in the plug again, the MDI swapping stopps again. If the MDI-swapping was in the "right" state I'm lucky and I get link. If not, removing and inserting the plug will eventually result in a link.

I double checked the schematics and the PCB layout but can't find any mistakes. Any ideas what could cause this behavior?

Regards,

Florian