Part Number: DP159RGZEVM

I have an issue with DP159 when setting DDC / HPD in snoop mode but no issue if DDC transits through active DDC block

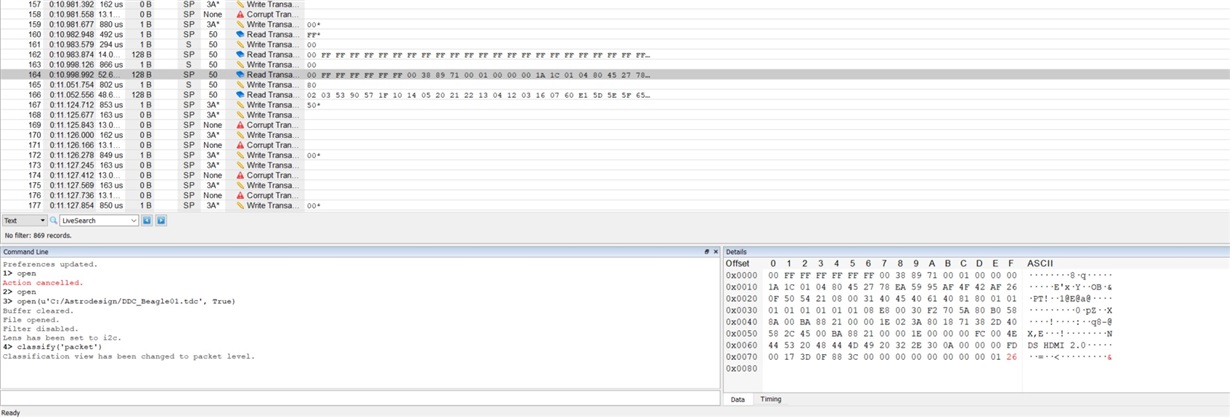

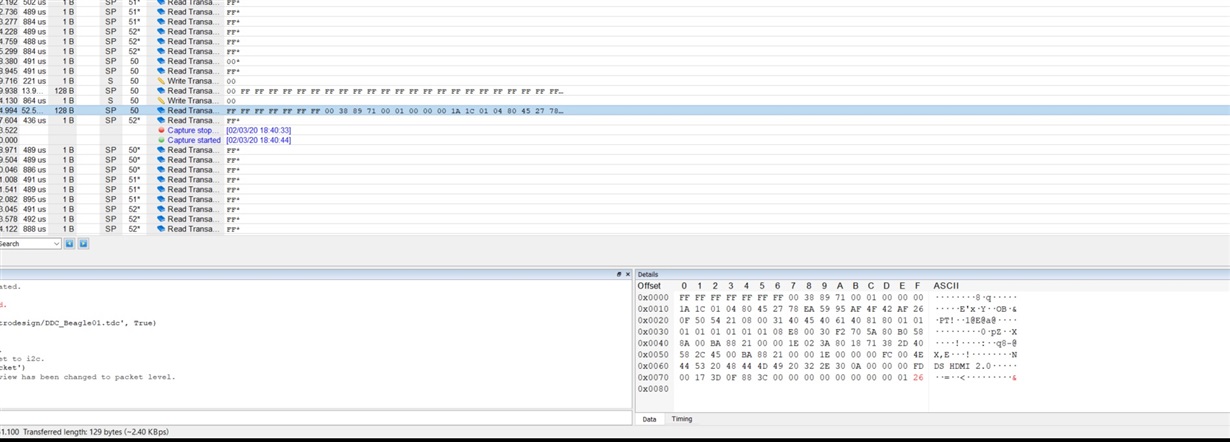

1. when DDC transits through active DDC block of DP159, HDMI 2.0 source (PC graphic card) signal in ON and I can see content on the display. Read back TMDS clock ratio = 1/40

2. when set DP159 as snoop on DDC interface, same HDMI 2.0 source shows no output and hence no content to display. Read back TMDS clock ratio = 1/10

Note that either active DDC or snoop DDC works OK when source is HDMI 1.4b

What difference can it make when DDC transits through DP159? Looking DDC traffic on the scope, there are more transactions when HDMI 2.0 source DDC info transits through DP159 than being snoop by DP159. Would it be the "true" sink of the HDMI 2.0 source and just conveys the info to the display? And why there are less transactions in snoop mode leading to HDMI 2.0 source with no output?

Last, I have no problem in either mode when I use the QD780E as HDMI 2.0 source

I hope someone had similar problem and can share the experience

Thanks

Lam Huynh