Part Number: TPS65983B

Other Parts Discussed in Thread: TPS65982

Hi,

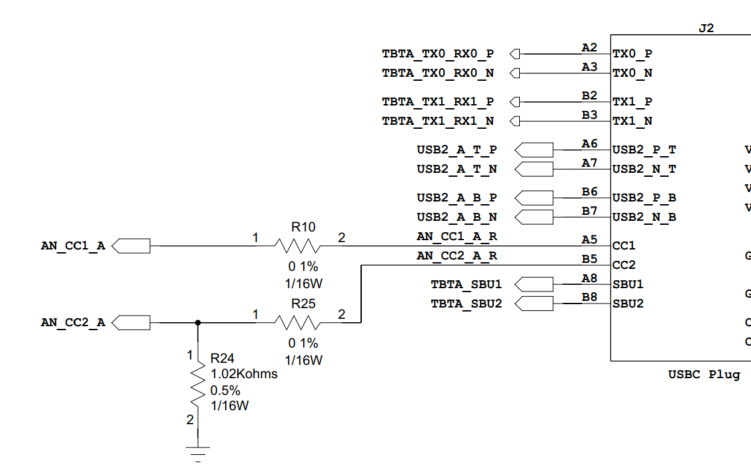

I have a loopback design based on Intel input for HVM. I have included a block diagram for clarity.

The design includes the TPS65983B PD controller and spi flash. There is no Thunderbolt device in the design.

I have built PD firmware using the TPS65983 Thunderbolt Application Customization Tool version 4.12. The firmware was built using the Bus-powered Device template.

This results in board power up and the loopback device "wakes-up" the USB3.1 Host controller in Alpine Ridge on a host system. I need it to "wake-up" the Thunderbolt Controller which is not happening.

My question is:

1. Is there a way to build the PD firmware so that the PD controller identifies itself as a Thunderbolt device?