Part Number: SN65DSI83-Q1

Other Parts Discussed in Thread: SN65DSI83, DSI-TUNER

Hello

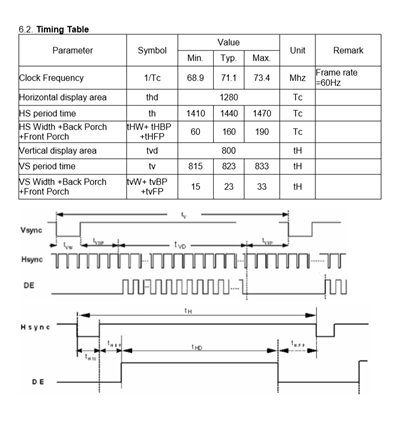

I would like run up SN65DSI83-Q1 with display, which timings is below.

PCB with bridge is our project, based on your eval board schematic and designed for 100 ohm impedance. Initialization is send via microcontroler and source DSI signal is from IMX8M.

Pattern from this IC works fine with clock LVDS from external crystal and DSI clock. When I would like convert DSI to LVDS is problem with stable screen – often screen is black and don’t refresh when source change image. Sometimes, when screen is almost as expect then I must wait for it about 5 secound and it is refresh from one edge. Next, when i change source image, display don't change image, so image is still the same. Other problem is with image in corners - is cut off (this problem don't occurs in pattern):

Can you check my initialization code ? Do you have any idea what I do wrong ?

Best regards,

Mateusz

#define SN65_reg_SOFT_RESET 0x09

#define SN65_reg_LVDS_CLK 0x0A

#define SN65_reg_MIPI_CLK 0x0B

#define SN65_reg_PLL_EN 0x0D

#define SN65_reg_CHA_DSI_LANES 0x10

#define SN65_reg_CHA_DSI_DATA_CLK 0x11

#define SN65_reg_CHA_DSI_CLK_RANGE 0x12

#define SN65_reg_LCD_SET 0x18

#define SN65_reg_LVDS_VOCM_VOD 0x19

#define SN_65_CHA_REVERSE_LVDS 0x1A

#define SN_65_CHA_LVDS_CM_ADJUST 0x1B

#define SN_65_CHA_ACTIVE_LINE_LENGTH_LOW 0x20

#define SN_65_CHA_ACTIVE_LINE_LENGTH_HIGH 0x21

#define SN_65_CHA_VERTICAL_DISPLAY_SIZE_LOW 0x24

#define SN_65_CHA_VERTICAL_DISPLAY_SIZE_HIGH 0x25

#define SN_65_CHA_SYNC_DELAY_LOW 0x28

#define SN_65_CHA_SYNC_DELAY_HIGH 0x29

#define SN_65_CHA_HSYNC_PULSE_WIDTH_LOW 0x2C

#define SN_65_CHA_HSYNC_PULSE_WIDTH_HIGH 0x2D

#define SN_65_DATA_TYPE 0x2E

#define SN_65_CHA_VSYNC_PULSE_WIDTH_LOW 0x30

#define SN_65_CHA_VSYNC_PULSE_WIDTH_HIGH 0x31

#define SN_65_CHA_HORIZONTAL_BACK_PORCH 0x34

#define SN_65_CHA_VERTICAL_BACK_PORCH 0x36

#define SN_65_CHA_HORIZONTAL_FRONT_PORCH 0x38

#define SN_65_CHA_VERTICAL_FRONT_PORCH 0x3A

#define SN_65_CHA_TEST_PATTERN 0x3C

#define SN_65_DSI_STRUCTURE_DATA_TYPE 0x3E

#define EXT_OSC

//#define MIPI_OSC

//#define PATTERN_ON

#define PATTERN_OFF

int sn65_init(void) {

HAL_GPIO_WritePin(SN65_EN_PORT, SN65_EN_PIN, GPIO_PIN_RESET);

HAL_Delay(10);

HAL_GPIO_WritePin(SN65_EN_PORT, SN65_EN_PIN, GPIO_PIN_SET);

HAL_Delay(10);

/*SOFT_RESET*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN65_reg_SOFT_RESET, 0x00);

/*PLL_EN_STAT, LVDS_CLK_RANGE, HS_CLK_SRC*/

#ifdef EXT_OSC

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN65_reg_LVDS_CLK, 0x04);

#endif

#ifdef MIPI_OSC

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN65_reg_LVDS_CLK, 0x05);

#endif

/*PLL_EN_STAT, LVDS_CLK_RANGE, HS_CLK_SRC*/

#ifdef EXT_OSC

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN65_reg_MIPI_CLK, 0x00);

#endif

#ifdef MIPI_OSC

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN65_reg_MIPI_CLK, 0x10);

#endif

/*PLL_EN set LOW - disable*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN65_reg_PLL_EN, 0x00);

/*CHA_DSI_LANES - 4lines*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN65_reg_CHA_DSI_LANES, 0x26);

/*SN65_reg_CHA_DSI_DATA_CLK*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN65_reg_CHA_DSI_DATA_CLK, 0xCC);

/*SN65_reg_CHA_DSI_CLK_RANGE*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN65_reg_CHA_DSI_CLK_RANGE, 0x2b);

/*SN65_reg_0x13, without description in DS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, 0x13, 0x00);

/*SN65_reg_LCD_SET format, mode, polarity DE, HS, VS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN65_reg_LCD_SET, 0x78);

/*SN65_reg_LVDS_VOCM_VOD*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN65_reg_LVDS_VOCM_VOD, 0x00);

/*SN_65_CHA_REVERSE_LVDS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_REVERSE_LVDS, 0x01);

/*SN_65_CHA_REVERSE_LVDS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_LVDS_CM_ADJUST, 0x00);

/*LVDS Pattern Generation*/

/*SN_65_CHA_ACTIVE_LINE_LENGTH_LOW*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_ACTIVE_LINE_LENGTH_LOW, 0x00);

/*SN_65_CHA_ACTIVE_LINE_LENGTH_HIGH*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_ACTIVE_LINE_LENGTH_HIGH, 0x05);

/*SN65_reg_0x22, without description in DS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, 0x22, 0x00);

/*SN65_reg_0x23, without description in DS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, 0x23, 0x00);

/*SN_65_CHA_VERTICAL_DISPLAY_SIZE_LOW*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_VERTICAL_DISPLAY_SIZE_LOW, 0x20);

/*SN_65_CHA_VERTICAL_DISPLAY_SIZE_HIGH*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_VERTICAL_DISPLAY_SIZE_HIGH, 0x03);

/*SN65_reg_0x26, without description in DS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, 0x26, 0x00);

/*SN65_reg_0x27, without description in DS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, 0x27, 0x00);

/*SN_65_CHA_SYNC_DELAY_LOW*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_SYNC_DELAY_LOW, 0x21);

/*SN_65_CHA_SYNC_DELAY_HIGH*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_SYNC_DELAY_HIGH, 0x00);

/*SN65_reg_0x2A, without description in DS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, 0x2A, 0x00);

/*SN65_reg_0x2B, without description in DS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, 0x2B, 0x00);

/*SN_65_CHA_HSYNC_PULSE_WIDTH_LOW*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_HSYNC_PULSE_WIDTH_LOW, 0x0A);

/*SN_65_CHA_HSYNC_PULSE_WIDTH_HIGH*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_HSYNC_PULSE_WIDTH_HIGH, 0x00);

/*SN_65_DATA_TYPE*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_DATA_TYPE, 0x00);

/*SN65_reg_0x2F, without description in DS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, 0x2F, 0x00);

/*SN_65_CHA_VSYNC_PULSE_WIDTH_LOW*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_VSYNC_PULSE_WIDTH_LOW, 0x05);

/*SN_65_CHA_VSYNC_PULSE_WIDTH_HIGH*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_VSYNC_PULSE_WIDTH_HIGH, 0x00);

/*SN65_reg_0x32, without description in DS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, 0x32, 0x00);

/*SN65_reg_0x33, without description in DS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, 0x33, 0x00);

/*SN_65_CHA_HORIZONTAL_BACK_PORCH*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_HORIZONTAL_BACK_PORCH, 0x46);

/*SN65_reg_0x35, without description in DS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, 0x35, 0x00);

/*SN_65_CHA_VERTICAL_BACK_PORCH*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_VERTICAL_BACK_PORCH, 0x08);

/*SN65_reg_0x37, without description in DS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, 0x37, 0x00);

/*SN_65_CHA_HORIZONTAL_FRONT_PORCH*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_HORIZONTAL_FRONT_PORCH, 0x50);

/*SN65_reg_0x39, without description in DS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, 0x39, 0x00);

/*SN_65_CHA_VERTICAL_FRONT_PORCH*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_VERTICAL_FRONT_PORCH, 0x09);

/*SN65_reg_0x3B, without description in DS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, 0x3B, 0x00);

/*SN_65_CHA_TEST_PATTERN*/

#ifdef PATTERN_ON

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_TEST_PATTERN, 0x11); //Pattern ON

#endif

#ifdef PATTERN_OFF

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_CHA_TEST_PATTERN, 0x00); //Pattern off

#endif

/*SN65_reg_0x3D, without description in DS*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, 0x3D, 0x00);

/*SN_65_DSI_STRUCTURE_DATA_TYPE*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN_65_DSI_STRUCTURE_DATA_TYPE, 0x00);

/*PLL_EN set LOW - enable*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN65_reg_PLL_EN, 0x01);

HAL_Delay(10);

/*SN65_reg_SOFT_RESET*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN65_reg_SOFT_RESET, 0x01);

HAL_Delay(10);

/*SN65_reg_SOFT_RESET - reset errors*/

SN65_reg_i2c_write_byte(SN65_I2C_ADDR_WRITE, SN65_ERR_reg, 0xFC);

return 1;

}