Hi Team,

I would like to ask the following questions.

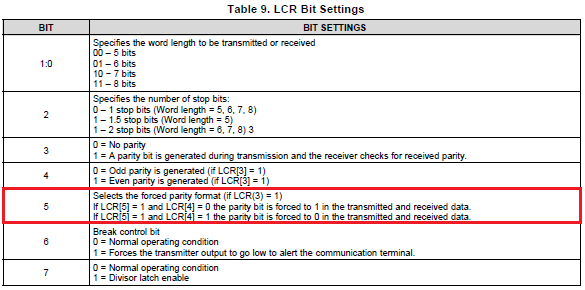

1) There is no description when LCR[5]=0. Is there any information?

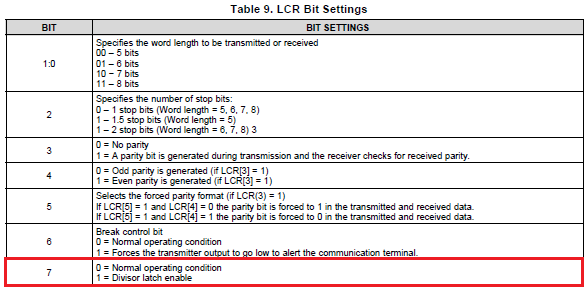

2) LCR[7] shows the following in datasheet.

Does "Divisor latch enable" indicate enabling the following operation?

(datasheet page 37)

8.5.12 Divisor Latches (DLL, DLH)

Two 8-bit registers store the 16-bit divisor for generation of the baud clock in the baud rate generator.

DLH, stores the most significant part of the divisor. DLL stores the least significant part of the division.

DLL and DLH can only be written to before sleep mode is enabled (that is, before IER[4] is set).

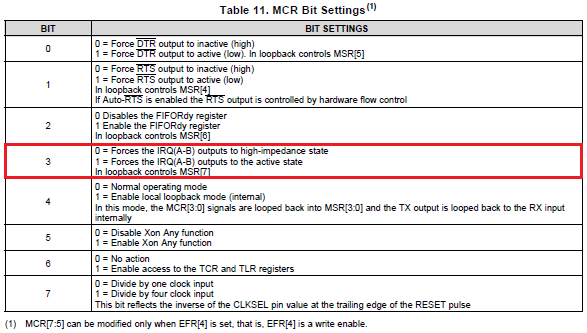

3) MCR[3] shows the following in datasheet.

Does IRQ(A-B) indicate INT(A-B)? There is no description about IRQ(A-B) in datasheet.

Best Regards,

Yaita

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.