Part Number: DP83825I

Hi,

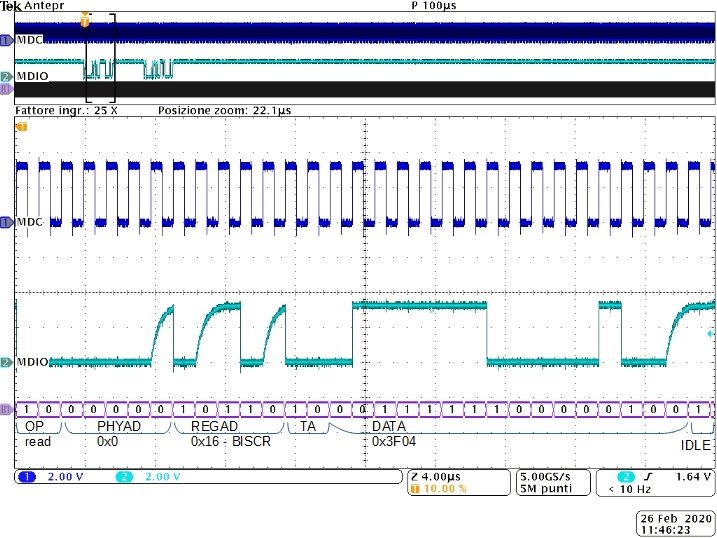

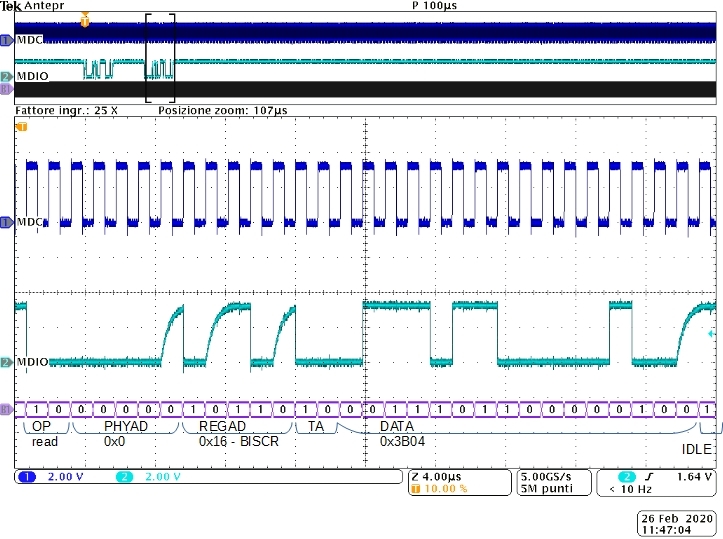

I'm trying to run BIST tests on DP83825I eth phy configured in 100Base-Tx mode.

I need to run all possible tests using the phy built-in functionalities only and when the board is not connected to the network.

1. Reading the datasheet at "7.3.15 BIST Configurations" paragraph and the BISCR [4-0] register description seems that I have to enable both PRBS generator and checker and that the only useful (for me) loopback modes are:

- 0x8 Analog loopback

- 0x4 Digital loopback

- 0x2 PCS Output loopback

Is it right?

2. Can I do this three tests sequentially? Or I have to reset and reconfigure the phy each test?

Regards,

Marco