Hello,

Our SerDes configuration is : DS90UB941 <=> DS90UB948

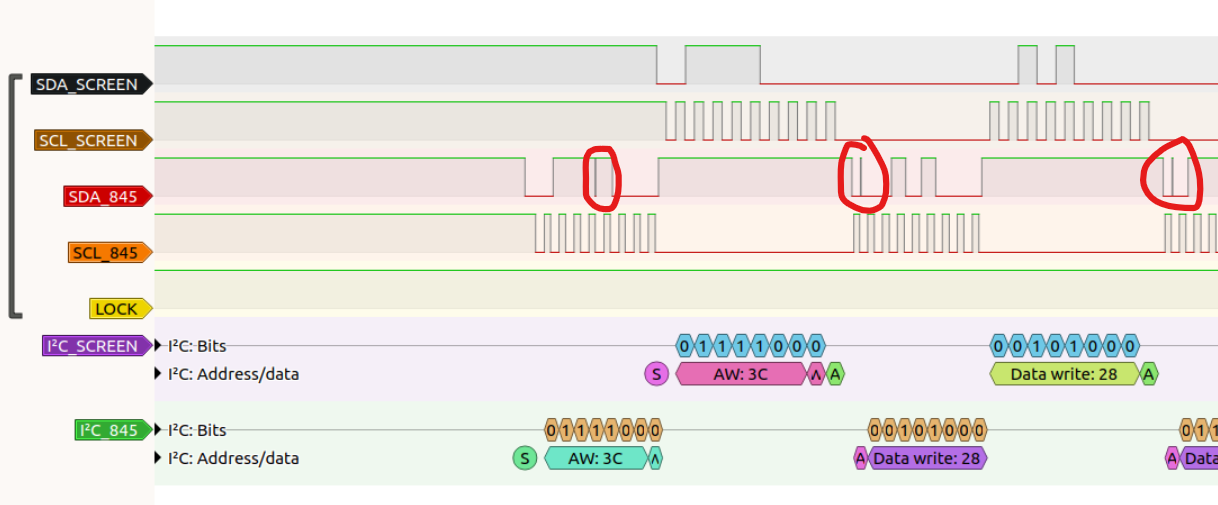

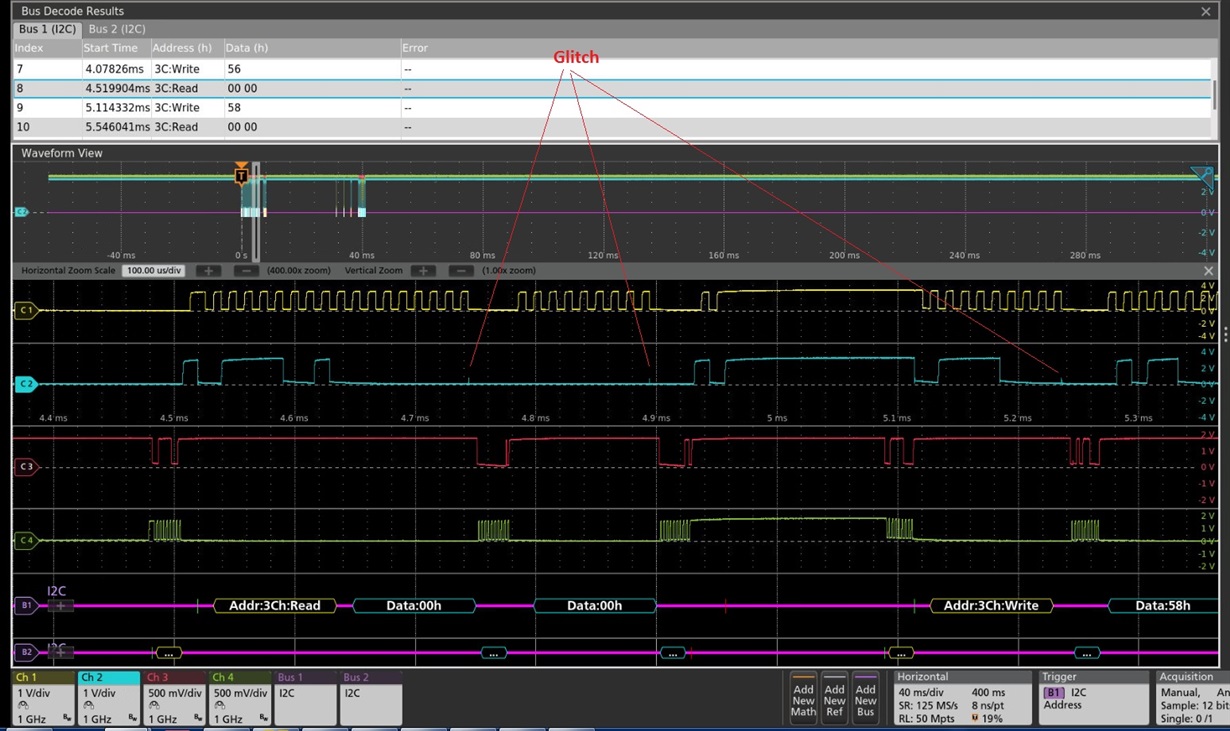

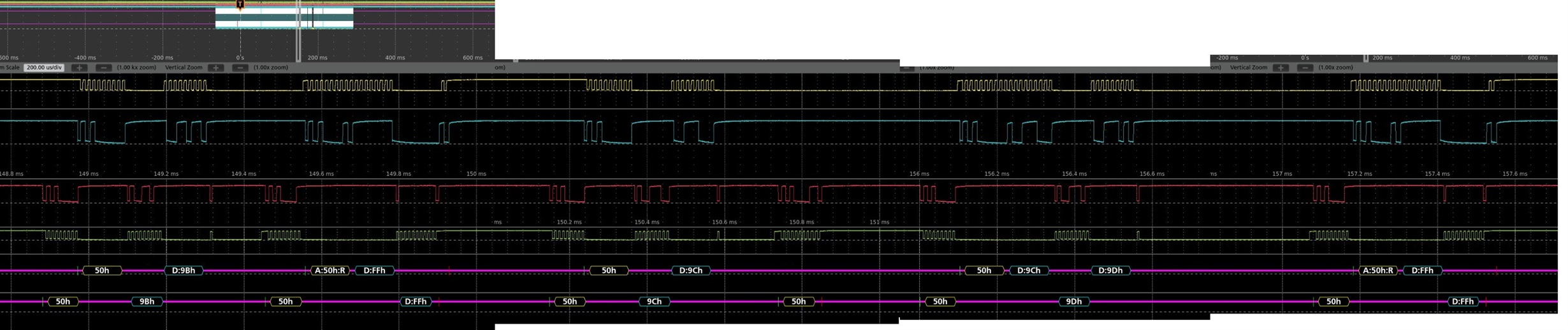

The I2C communication between serializer and deserializer is not constant.

-

sdm845:/ # i2cdetect -y -r 2

-

0 1 2 3 4 5 6 7 8 9 a b c d e f

-

00: -- -- -- -- -- -- -- -- -- 0c -- -- --

-

10: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

-

20: -- -- -- -- -- -- -- -- UU -- -- -- UU -- -- --

-

30: -- -- -- -- -- -- -- -- -- -- -- -- 3c -- -- --

-

40: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

-

50: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

-

60: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

-

70: -- -- -- -- -- -- -- --

-

sdm845:/ # i2cdetect -y -r 2

-

0 1 2 3 4 5 6 7 8 9 a b c d e f

-

00: -- -- -- -- -- -- -- -- -- 0c -- -- --

-

10: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

-

20: -- -- -- -- -- -- -- -- UU -- -- -- UU -- -- --

-

30: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

-

40: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

-

50: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

-

60: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

-

70: -- -- -- -- -- -- -- --

-

sdm845:/ # i2cdetect -y -r 2

-

0 1 2 3 4 5 6 7 8 9 a b c d e f

-

00: -- -- -- -- -- -- -- -- -- 0c -- -- --

-

10: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

-

20: -- -- -- -- -- -- -- -- UU -- -- -- UU -- -- --

-

30: -- -- -- -- -- -- -- -- -- -- -- -- 3c -- -- --

-

40: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

-

50: 50 -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

-

60: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

-

70: -- -- -- -- -- -- -- --