Part Number: LMH1228

Other Parts Discussed in Thread: SIGCONARCHITECT

Hello team,

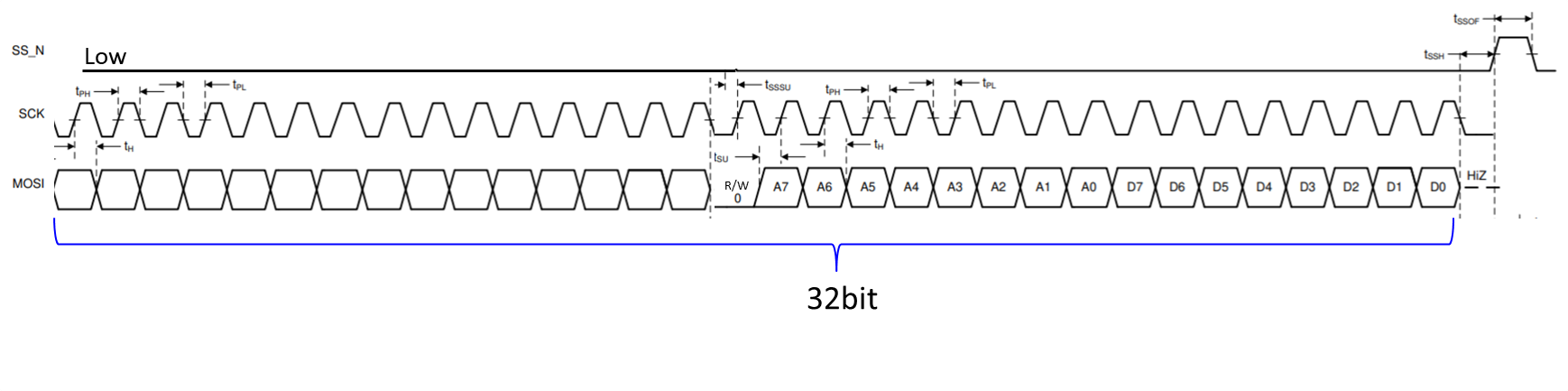

IP core in customer's FPGA only can handle 32bit length data for SPI, not 17bit length.

If R/W bit, address and data are put on last 17bits like below, can LMH1228 communicate properly with processor?

SS_N is pulled LOW before sending 32bit data and pulled high just after end the 32bit data.

Regards,

Saito