Part Number: THVD1450

Hello

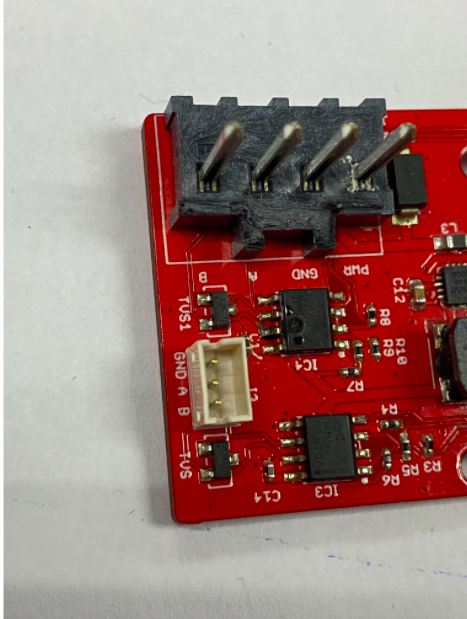

We have a designed and tested a few boards with THVD1450. The boards work well, but every now and then at power up, we see the THVD1450 chip on the board get hot and sometimes even burn out. Attached is a picture. IC4 is THVD1450. Pin A was shorted to ground. all regulators on board worked fine. When the part was desoldered the short went away.

After some debug on the board, we felt that its an issue with just the THVD1450 - a possible latch up issue because it happens only during the first few minutes of start up. After digging through the data sheet, I noticed the following.

Page 29 of the datasheet, layout guidelines #7, which mentions the following

"Insert pulse-proof resistors into the A and B bus lines if the TVS clamping voltage is higher than the specified maximum voltage of the transceiver bus pins. These resistors limit the residual clamping current into the transceiver and prevent it from latching up."

Figure 37 on the datsheet also shows these pulse proof resistors that we have not placed in our design. I have the SM712 ESD part which gives a clamping voltage of ~19 for a 1A current.

In light of this we are going to change the design to place these resistors, but I wanted to do a quick check in with the experts at TI to make sure that this issue of THVD1450 burn up is indeed a latch up issue because of the lack of pulse proof resistor or could it be sign of something else? I'm guessing the application engineers at TI must have seen similar issues like this?

Thanks

Raghu