Hi Team,

There are two questions may need your help..

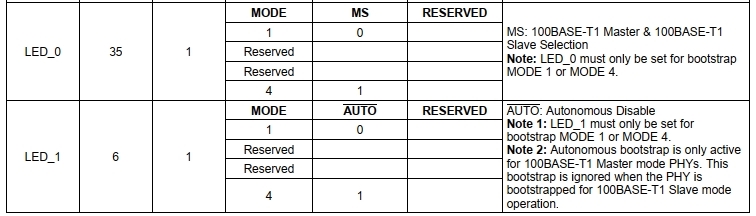

- When using SGMII mode, how to configure master or slave? Customer has tried P46 in datasheet to configure LED0 and LED1 but failed.

Maybe I could just ask them to configure by setup PMA_CTRL2 Register 0x0834 – MMD1 PMA Control Register #2?

- If in the same PHY, hardware set as slave but software set as salve, which mode actually the PHY is? Master or Salve?

Will it cause software return error? Customer now receive such a error:"Kernel log shows that the clock between phy and MAC is not on lock; sgmii CDR not lock"