Hello,

my customer is currently working on a project with SER_933 and DES_954 and he has a question.

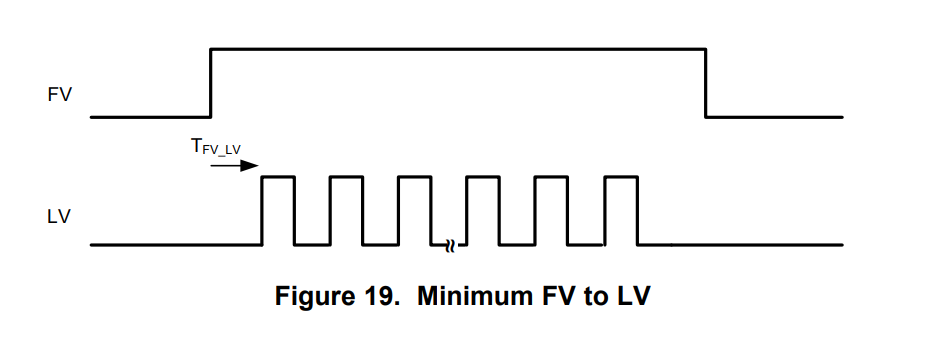

I copy here a graph from the chapter 7.4.14 of the Deserializer Spec 954:

In this chapter it is described the frame-start pretty precisely. When the deserializer 954 is used with a 933 Serializer, special requirements for TFV_LV are needed, see table 11 in this chapter.

The timing for frame-start is understood, but:

What timing is allowed in the frame end?

Is in the frame-end a minimum timing needed like in the beginning (frame_start)? If yes, what is the minimum timing here?

What happens, when FV is switched off too early (before LV is switched off)? Is there also a minimum time we have to take care of?

Best regards,

Stani