Part Number: DS90UH947-Q1

Other Parts Discussed in Thread: ALP

Hi Team,

My customer is using DS90UH947-Q1 / 948 and their display to test the pattern generation test.

They refer http://www.ti.com/lit/an/snla132e/snla132e.pdf And they have a issue showing on display. (Afther 5 mins, the display is somehow flicker, the phenomenon isn't frequently.)

Pattern selection : Full-screen User-Configurable Color (Gray scale)

We think the issue is from timing setting from 947. Could you let us know the rule of serializer register setting when the display spec is showing as below.

Display spec.

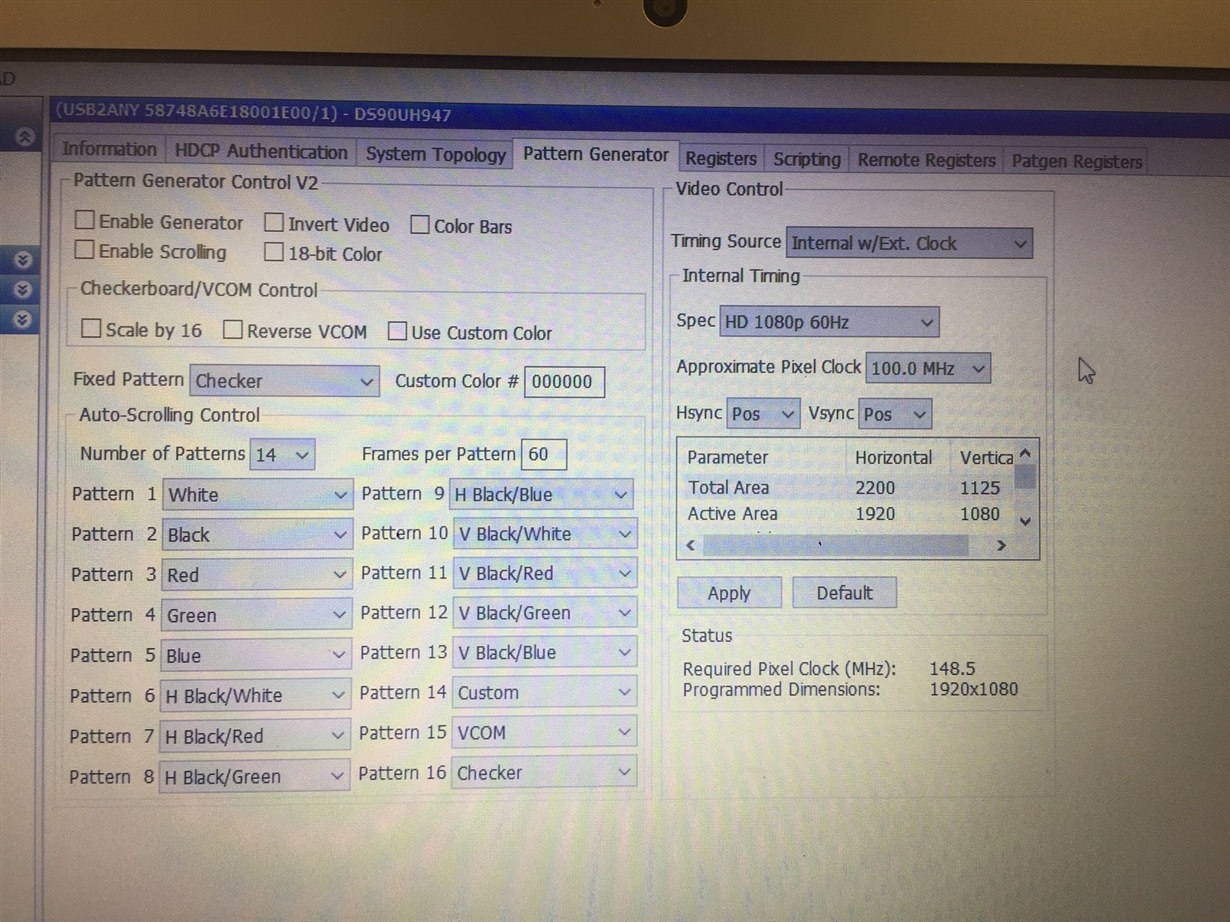

Current setting.

uint8_t serInitCode6[] = {0x4f, 0x40};

uint8_t serInitCode7[] = {0x66, 0x07};

uint8_t serInitCode8[] = {0x67, 0x80};

uint8_t serInitCode9[] = {0x66, 0x08};

uint8_t serInitCode10[] = {0x67, 0x07};

uint8_t serInitCode11[] = {0x66, 0x09};

uint8_t serInitCode12[] = {0x67, 0x4B};

uint8_t serInitCode13[] = {0x66, 0x04};

uint8_t serInitCode14[] = {0x67, 0xB2};

uint8_t serInitCode15[] = {0x66, 0x05};

uint8_t serInitCode16[] = {0x67, 0x07};

uint8_t serInitCode17[] = {0x66, 0x06};

uint8_t serInitCode18[] = {0x67, 0x4C};

uint8_t serInitCode19[] = {0x66, 0x0C};

uint8_t serInitCode20[] = {0x67, 0x19};

uint8_t serInitCode21[] = {0x66, 0x0D};

uint8_t serInitCode22[] = {0x67, 0x05};

uint8_t serInitCode23[] = {0x66, 0x0A};

uint8_t serInitCode24[] = {0x67, 0x0A};

uint8_t serInitCode25[] = {0x66, 0x0B};

uint8_t serInitCode26[] = {0x67, 0x01};

uint8_t serInitCode27[] = {0x66, 0x0E};

uint8_t serInitCode28[] = {0x67, 0x00};

Bist_P_num=0x11;

uint8_t serInitCode29[] = {0x65, 0x0C};

uint8_t serInitCode30[] = {0x64, Bist_P_num};

Thank you for your support.

Regards,

Roy