Part Number: DP83867CS

Hi Sir,

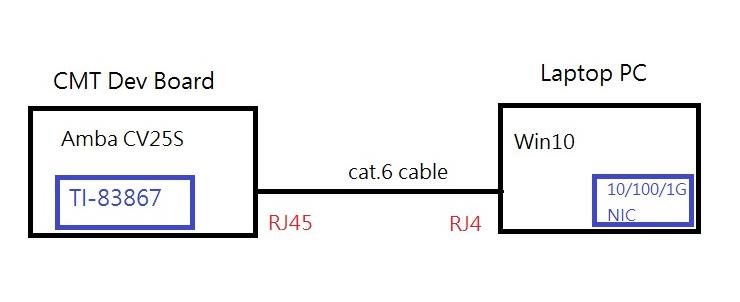

My customer working on TI DP83867 Ethernet PHY bring-up this week.

Right now, we can see eth0 in Linux but can’t get any response by ping.

1. The frequency of CLK_OUT is 25MHz.

It should be 125MHz because of RGMII.

Do we need to change register IO_MUX_CFG (0x170) setting?

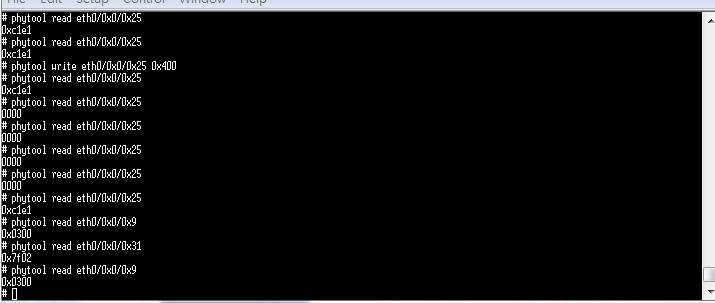

2. MDIO seems not work?

The read back phy id (through function: get_phy_id()) is always 0.

But from the driver, it should be 0x2000a231.

I’m not sure is it the root cause, so dp83867 (phy_driver) can’t attach to the phydev->mdio.dev.driver.

It turns out that genphy_driver was registered in function: phy_attach_direct().

3. I check the source code and the spec, the device address is 0x1f.

Should I assign this address to .dts?

As my customer response, TI helped one of their customer bring up DP83867 on AMBA CV22 chip last week.

Please help us figure out the root cause.

===

This is what I change:

1. built-in linux-4.14/drivers/net/phy/dp83867.c into Linux kernel

2. define mac0 in .dts.

mac0: ethernet@e000e000 {

status = "ok";

pinctrl-0 = <&rgmii_pins>;

/*amb,ahb-12mhz-div = <5>;*/

amb,tx-clk-invert;

/*amb,int-gtx-clk125;*/

/*amb,ext-ref-clk;*/

phy-mode = "rgmii";

phy@0 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <31>; ß should I assign 31 (0x1f) here?

rst-gpios = <&gpio 25 0>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_25_NS>;

ti,tx-internal-delay = <DP83867_RGMIIDCTL_2_75_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

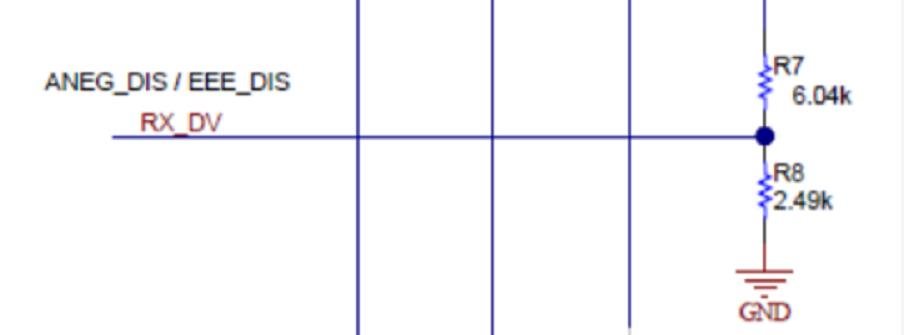

ti,dp83867-rxctrl-strap-quirk;

enet-phy-lane-swap;

};

};

Thanks, Ian.