Part Number: TS2PCIE2212

Other Parts Discussed in Thread: HD3SS3212

// for TSPCIE2212 IC, I don't read the spec deeplu, I just selected for writing this question.

Hi TI,

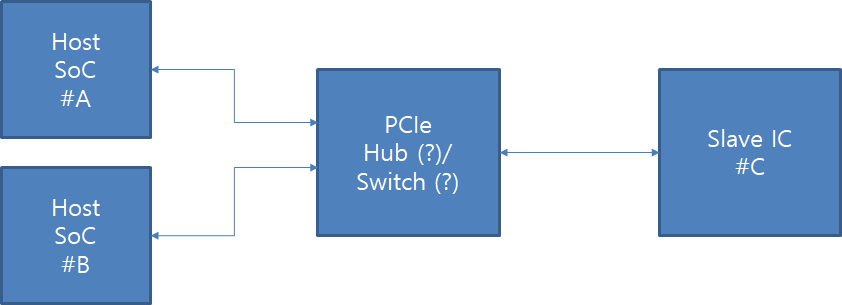

I have a question for below figure.

is there any PCIe switch (or hub) to access Slave ICs for each SoCs ?

Thanks