Other Parts Discussed in Thread: DSI-TUNER

Hi TIer,

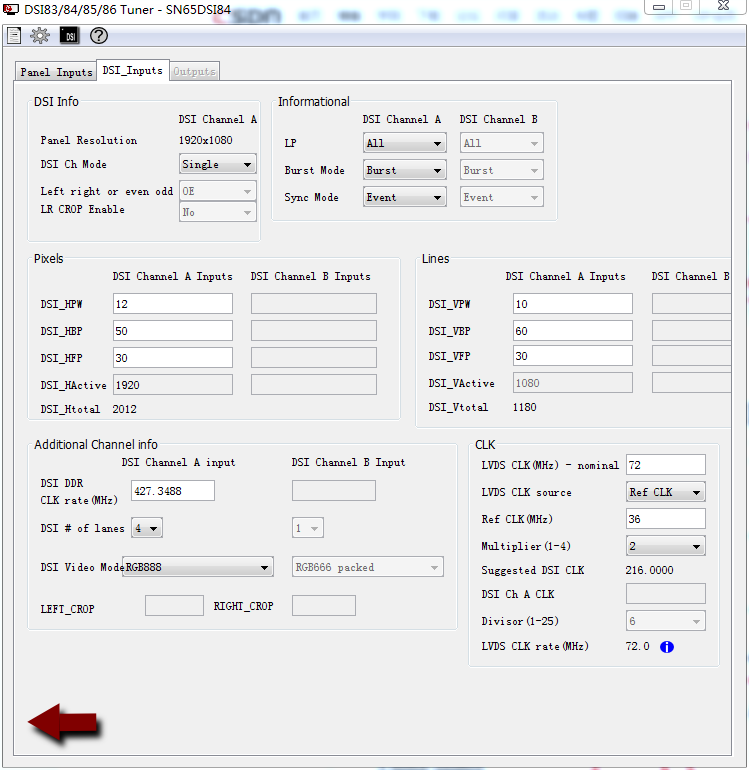

After I initialized the register according to the DSS, if I judge the A.7 (PLL LOCKED) bit, I find that it will never be set to 1, which means there is no way to LOCK problem? ?

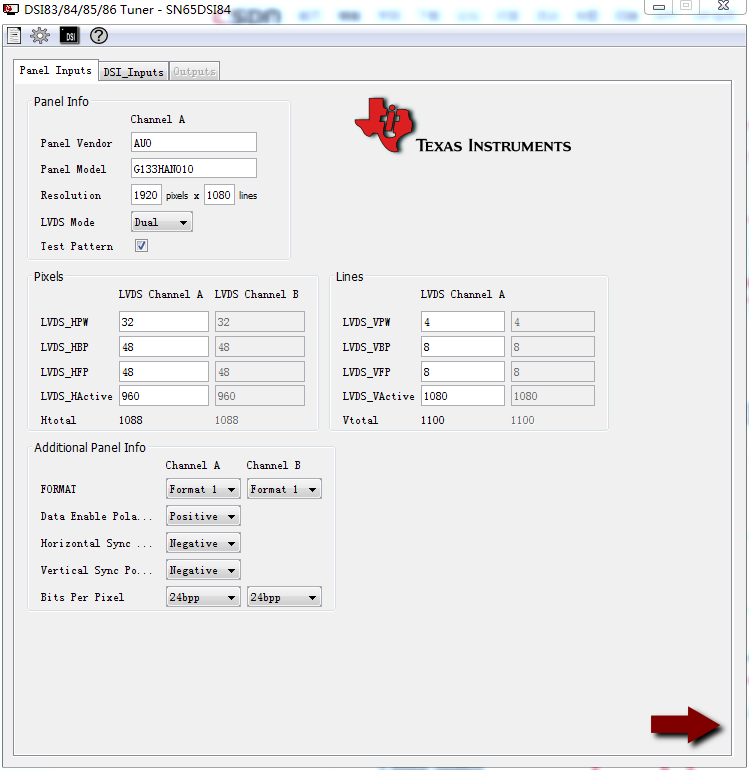

I 'm design REF CLK connected to 36MHz active crystal.