Part Number: TCAN1043-Q1

Other Parts Discussed in Thread: TCAN1043

Hi all,

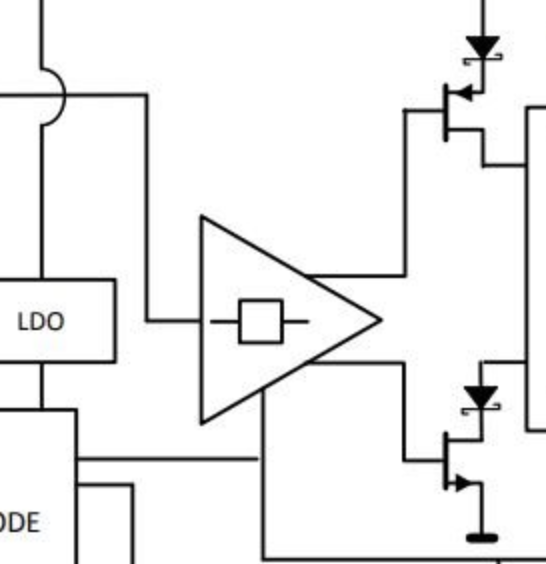

This is TCAN1043 Block Diagram.

I had some questions, while I looked the datasheet.

Could you please explain what and how the "Biass Unit" Box works?

What is the "WUP Detect"?

Can you explain me how the MUX works in this block diagram?

Thank you.