Other Parts Discussed in Thread: DP83TC811

Hi Team,

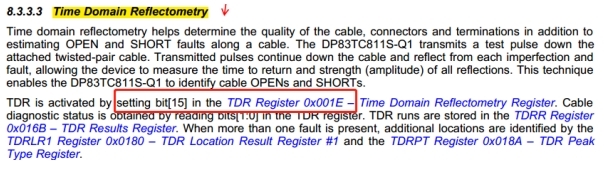

DP83TC811S-Q1 was test in customer side. Now they have a problem on TDR test enable procedure. Customer can't enable TDR test.

Here is the action they did, could you check it for us and provide the right TDR test enable procedure? Thanks.

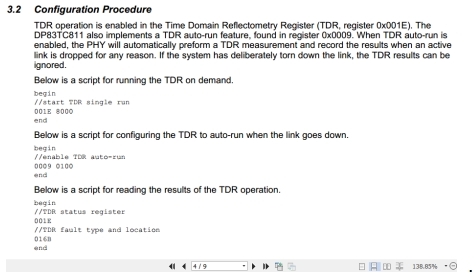

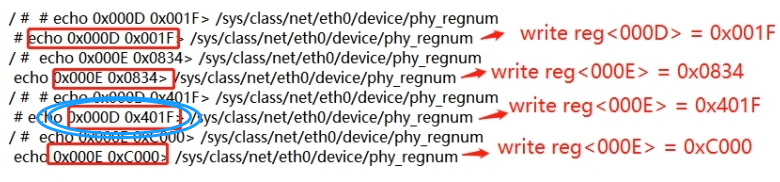

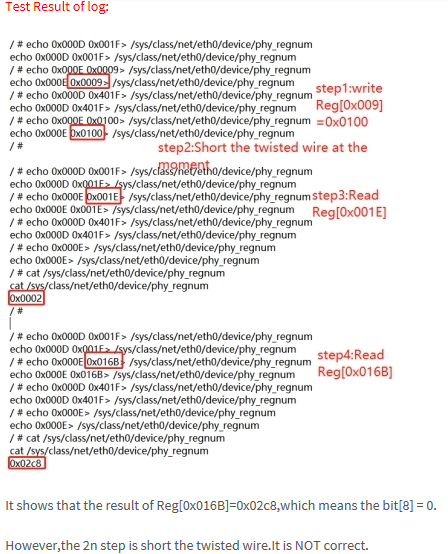

Step1: Enter Managed operation mode, write 0x0000 to register 0x018B;

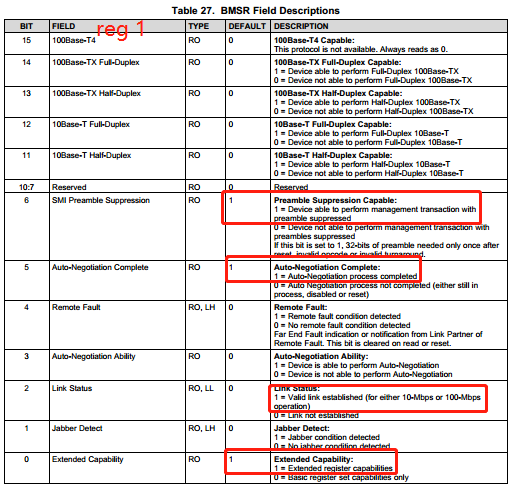

Step 2: Start TDR test, Write 0x8000 to register 0x0001e;

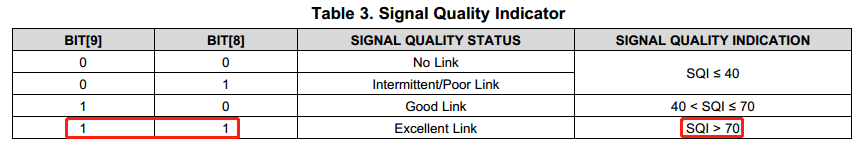

Step 3: Short Cable or Open Cable;

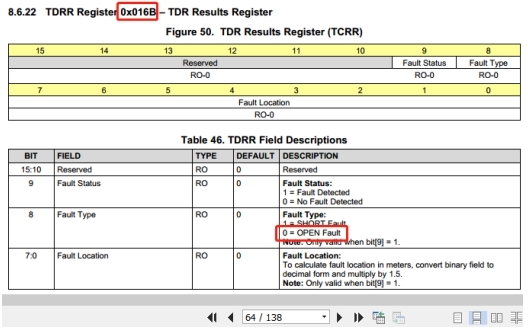

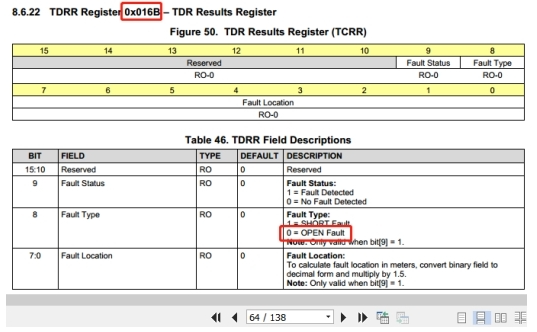

Step4: Read the value of register 0X016B, but the value is 0x0000.

BR

Songzhen Guo