Part Number: DP83867E

Hello,

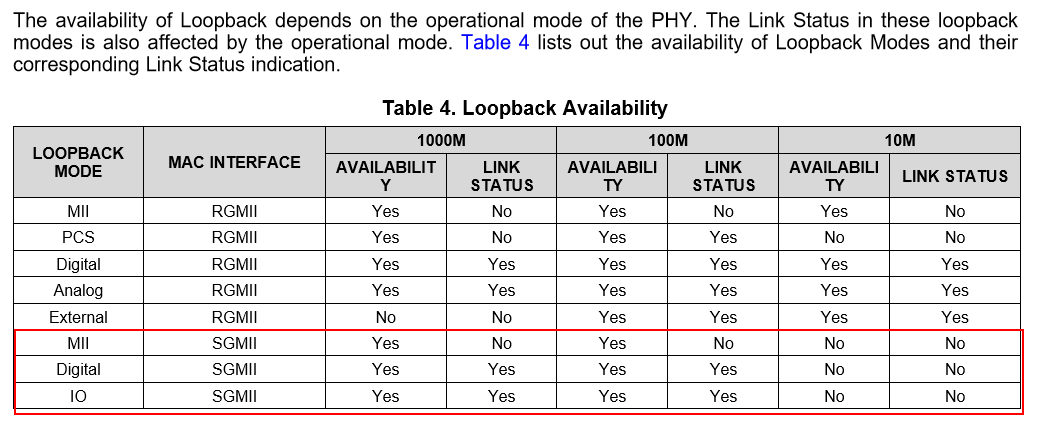

Switch and PHY 83867 interface are SGMII, switch-> PHY is tested by Digital Loopback, I can link up to detect link status is also set, but after closing loopback, the link has not been connected, the initial problem may be PHY-> RJ45-> PC, I would like to ask you which PHY-> RJ45-> PC, which registers do I need to operate?

THANKS

Best regards!