Part Number: SN65DSI84

Other Parts Discussed in Thread: DSI-TUNER

Hello experts,

Our NXP i.MX8MQ project uses the SN65DSI84 to convert MIPI to LVDS signals.

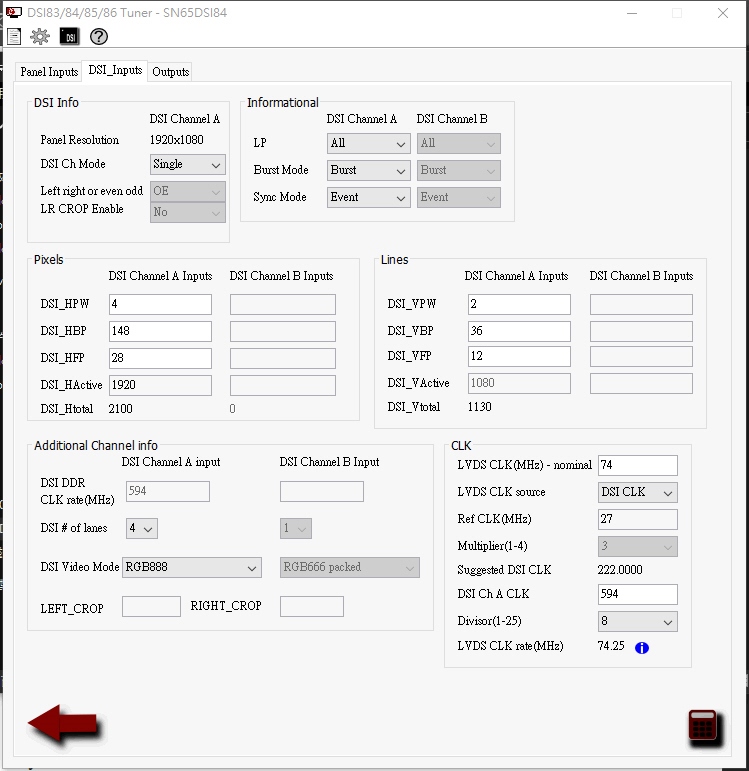

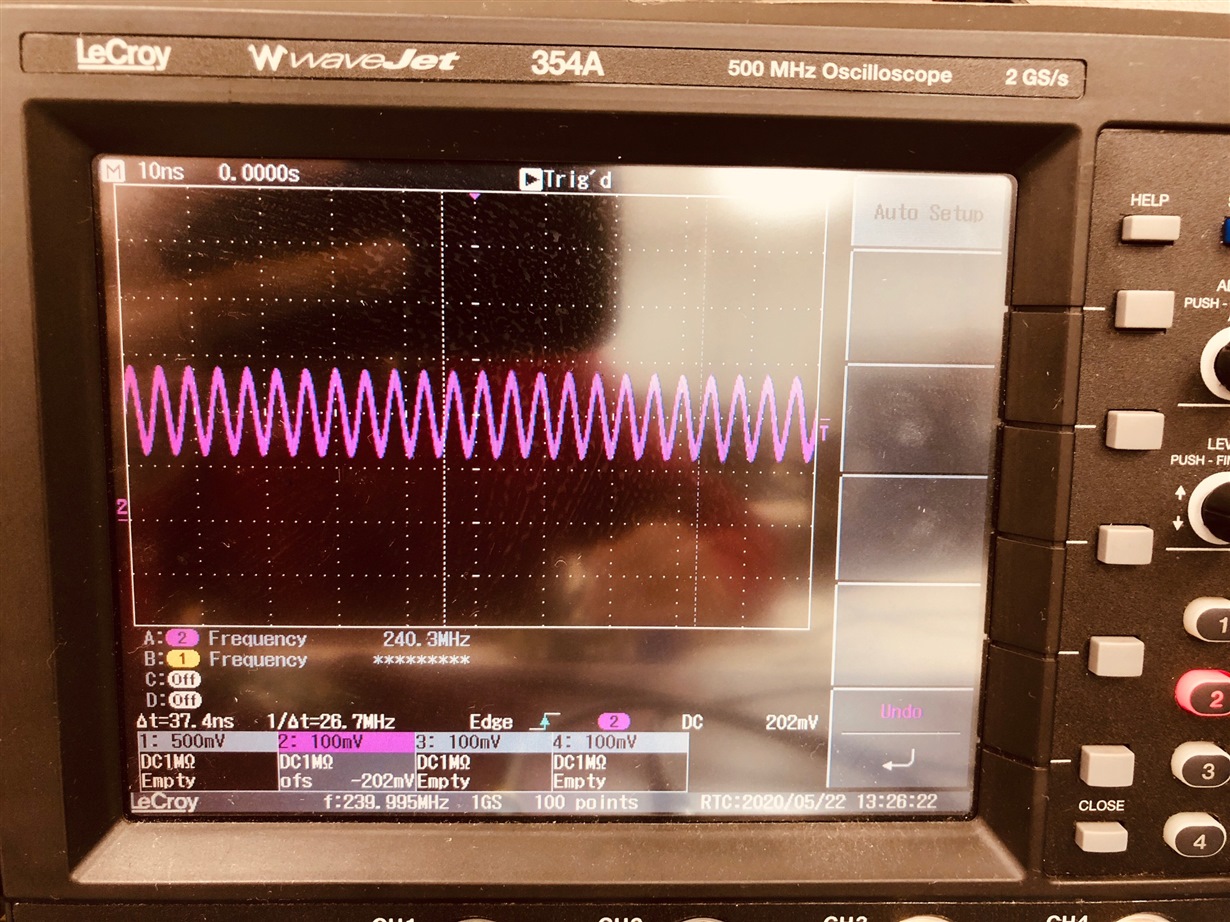

We tried to use DSI_Tuners to generate all register setting and enable Reg-3ch = 0x10 to output test pattern, but it failed and the Reg-e5 = 0x7d.

We also tried to use DSICLK and REFCLK to do the same test, but the test pattern cannot be outputed to panel.

Could please help to review our settings.

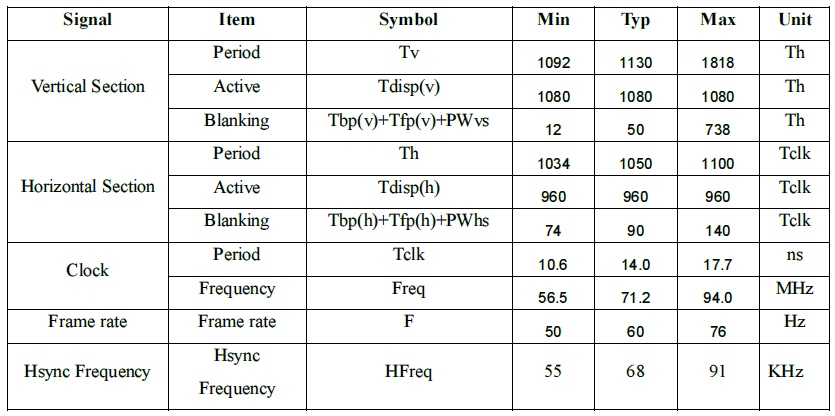

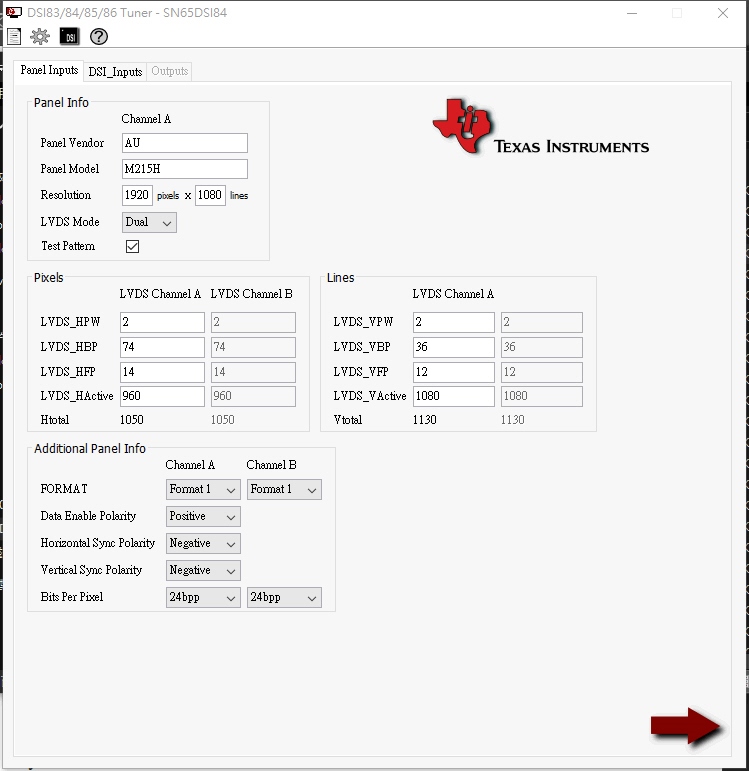

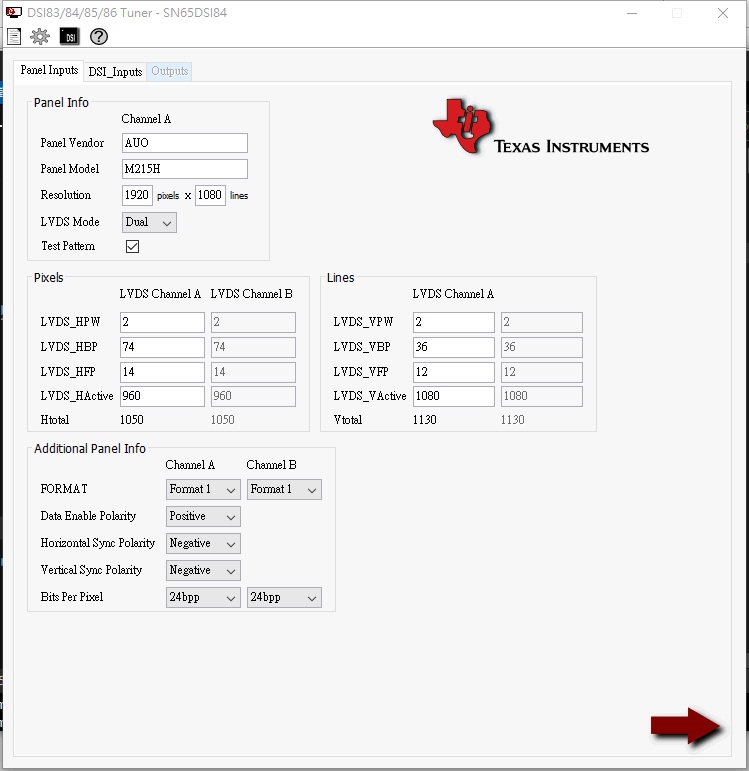

(1) Is it correct for AU-M215H 1920 x 1080 panel parameters? (http://www.bfdisplay.fr/fiches-techniques/ecrans-tft/AUO%20-%20M215HTN01_V1.pdf)

LVDS_HPW = 2

LVDS_HBP = 74

LVDS_HFP = 14

LVDS_VPW = 2

LVDS_VBP = 36

LVDS_VFP = 12

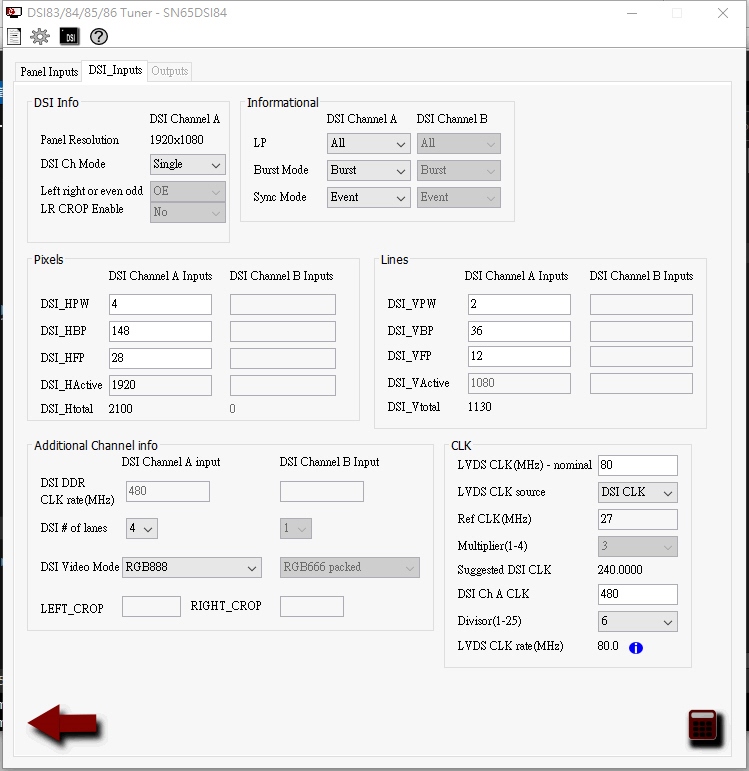

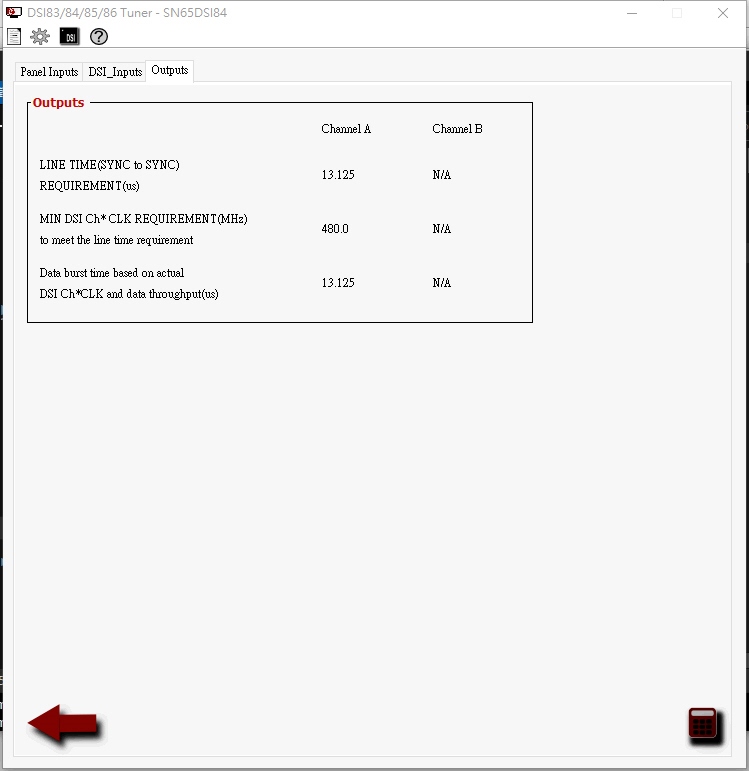

(2) Using DSI_Tuner to generate SN65DSI84 register settings.

Regards,

Mark