Part Number: XIO2001

Currently developing the XIO2001 to replace a design going EOL. Having difficulty troubleshooting the XIO2001. Attached are a few oscilloscope images (A) PCI_CLK (B) Power-up sequence.

A. Below is an image of the PCI_CLK. This signal is present at both PCI slots as well as the PCI_FBCLK. We have the EVM so I know the negative swing of the CLK is expected, but not the distortions.

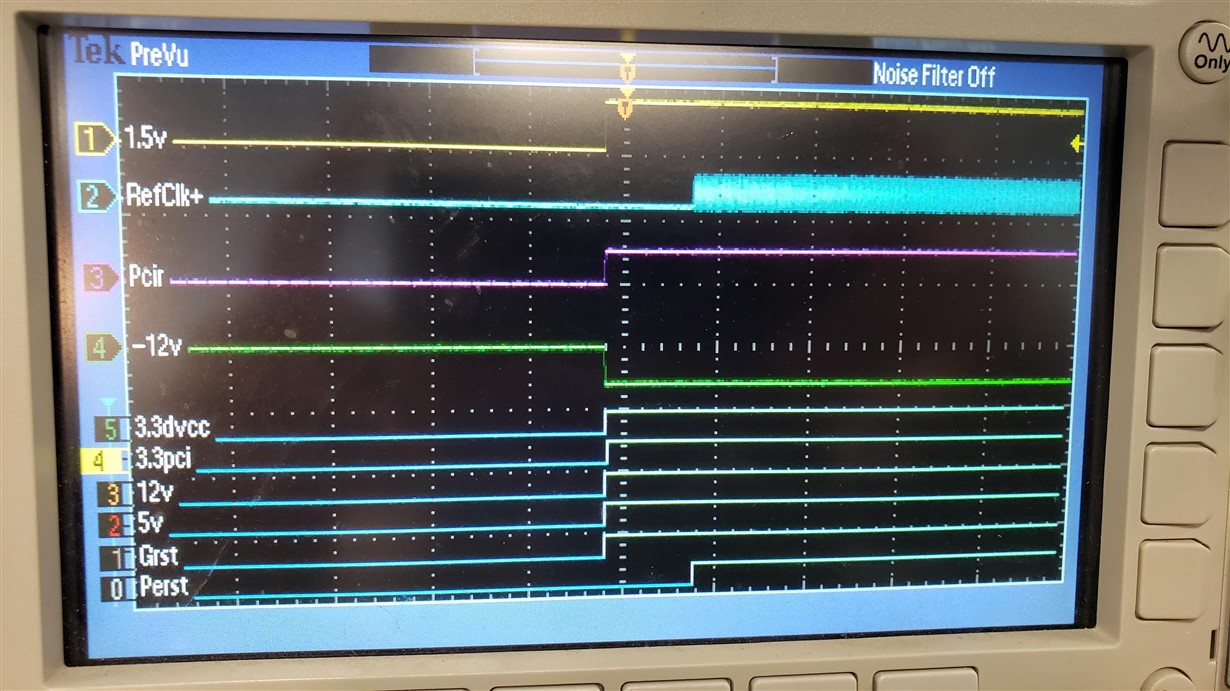

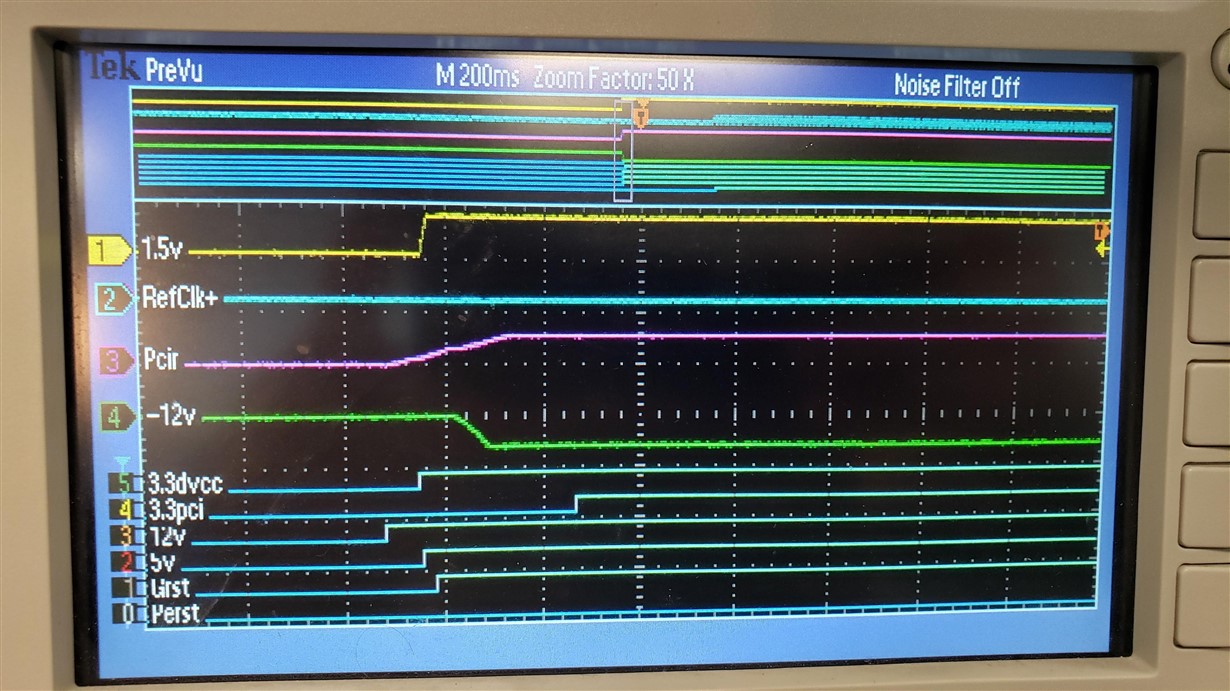

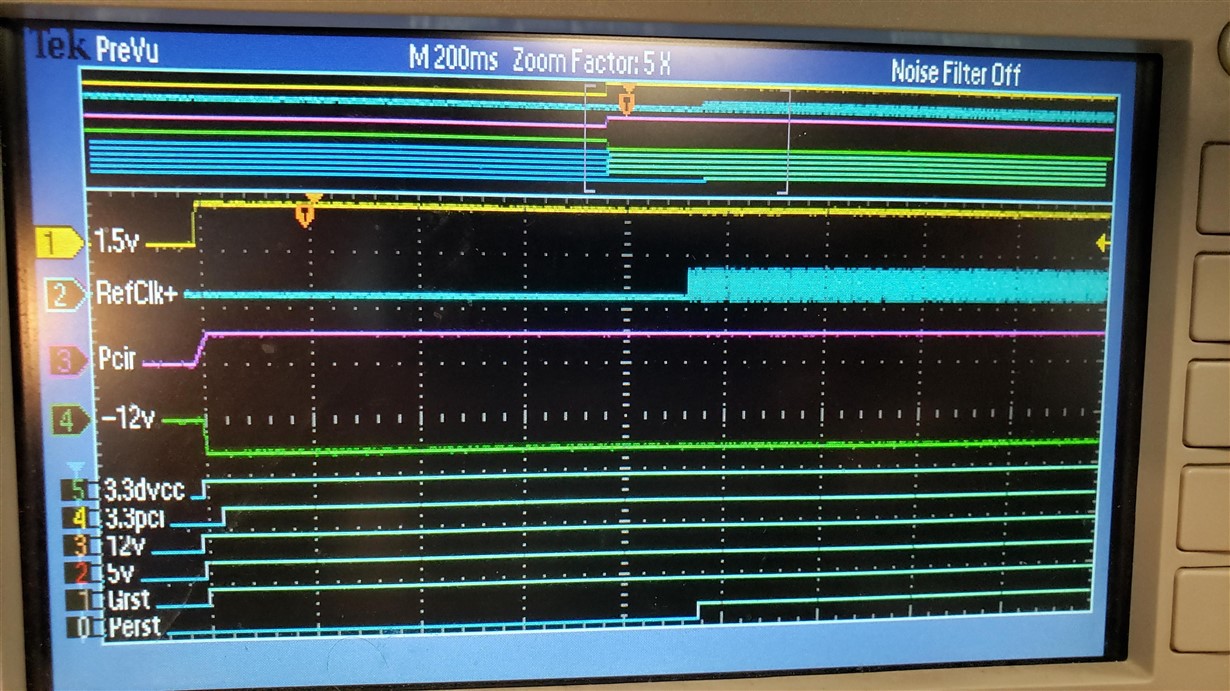

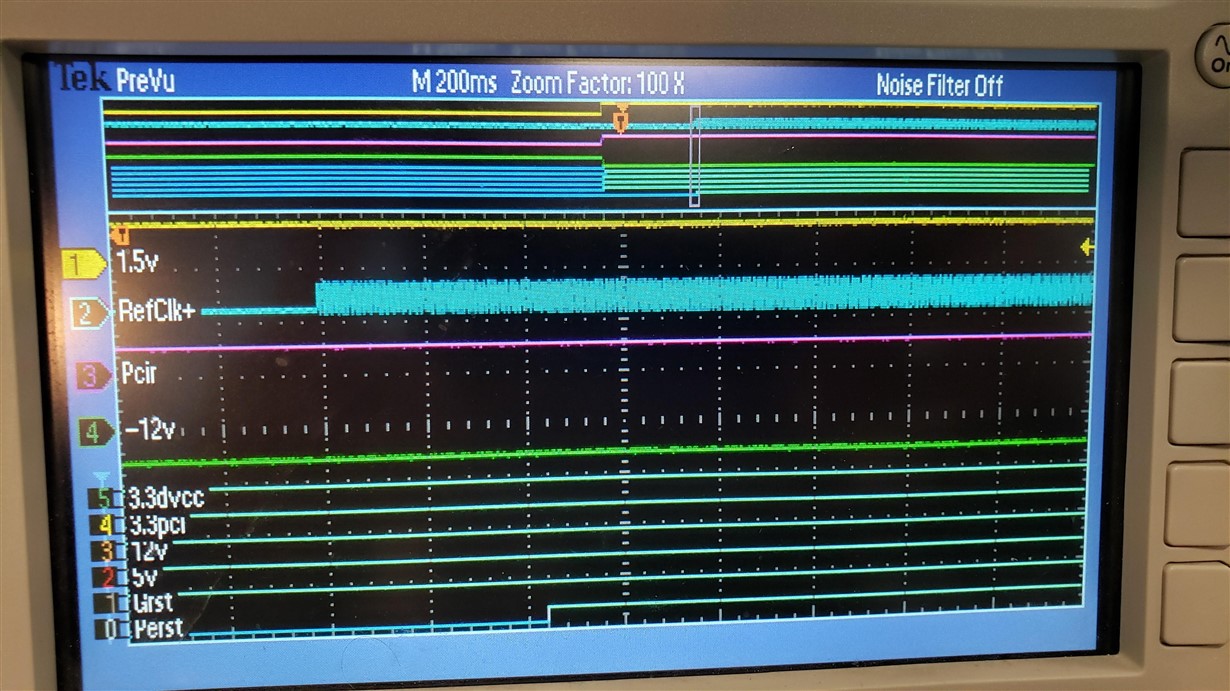

B. Below is the power-up sequence. Yellow = 1.5Vdc. Cyan = nGRST. Magenta = nPERST. Lime = REFCLK+.

I believe the oscillation seen on the 1.5Vdc rail at the beginning of REFCLK+ is a probe grounding issue and not the coupling of REFCLK+ to the power rail.

Based on my understanding, these are in order and the minimum timing requirements are greatly exceeded.

I have a hunch the board house did not properly perform requested impedance matching as they also changed our requested copper thicknesses.

What could cause the distortions on PCI_CLK? Would the distortions on the CLK prevent the XIO2001 from being discovered by the PC? Additionally, could this also prevent the PC from booting? Half of the ordered boards do not allow the PC to boot.

I would be more than happy to share schematics or board layout via email. Any help or input will be greatly appreciated.

Thank you.