Part Number: TSB43AB23

Dear all,

I would like to ask about read cycle of TSB43AB23.

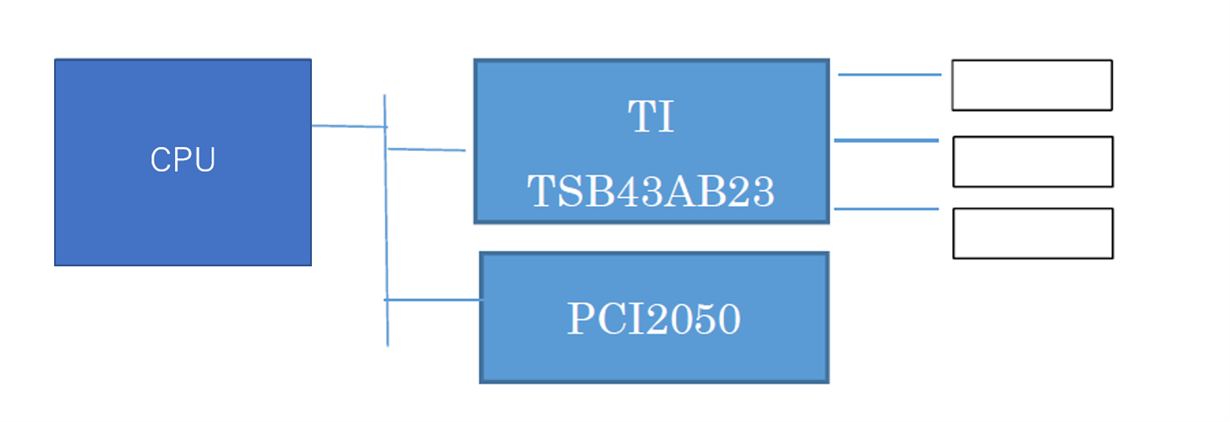

TSB43AB23 from CPU (Master). (PCL_CLK is set to 33MHz)

From the PCI bus side of the CPU, when the single access to the PCI bus space of the TSB43AB23 connected to the PCI bus was continuously performed, it became as follows.

-When I made a single access of about 64 bytes, it was accessed correctly.

-When a single access of about 256 bytes was performed, the CPU side recognized that the PCI bus access took too long and timed out.

To investigate the above cause, they confirmed the waveforms of the IRDY signal output from the CPU on the PCI bus and input to the TSB43A23 and the TRDY signal output from the TSB43AB23 and input to the CPU. By doing this, they measured how long it took for the target device to respond to the read request from the master device.

The result is as follows.

-When performing a single access with 64 bytes, there was a response from TSB43AB23 after 5 cycles of PCI_CLK (30ns x 5clk = 150ns when PCI_CLK is 33MHz) after IRDY goes Low. At that time, IRDY returned to HIgh.

-When single access was performed with 256 bytes, TSB43AB23 responded after 23 cycles of PCI_CLK (30ns x 23clk = 690ns when PCL_CLK is 33MHz) after IRDY became Low. At that time, IRDY returned to HIgh.

It is considered that the CPU side decided that "23 cycles of PCI_CLK" was "long" and timed out as described above. The TSB43AB23 normally responds in about 5 cycles of PCI_CLK, but why does the read cycle become long up to “23 cycles of PCI_CLK”?

Best Regards,

Y.Ottey