Other Parts Discussed in Thread: SIGCONARCHITECT

Dear e2e support,

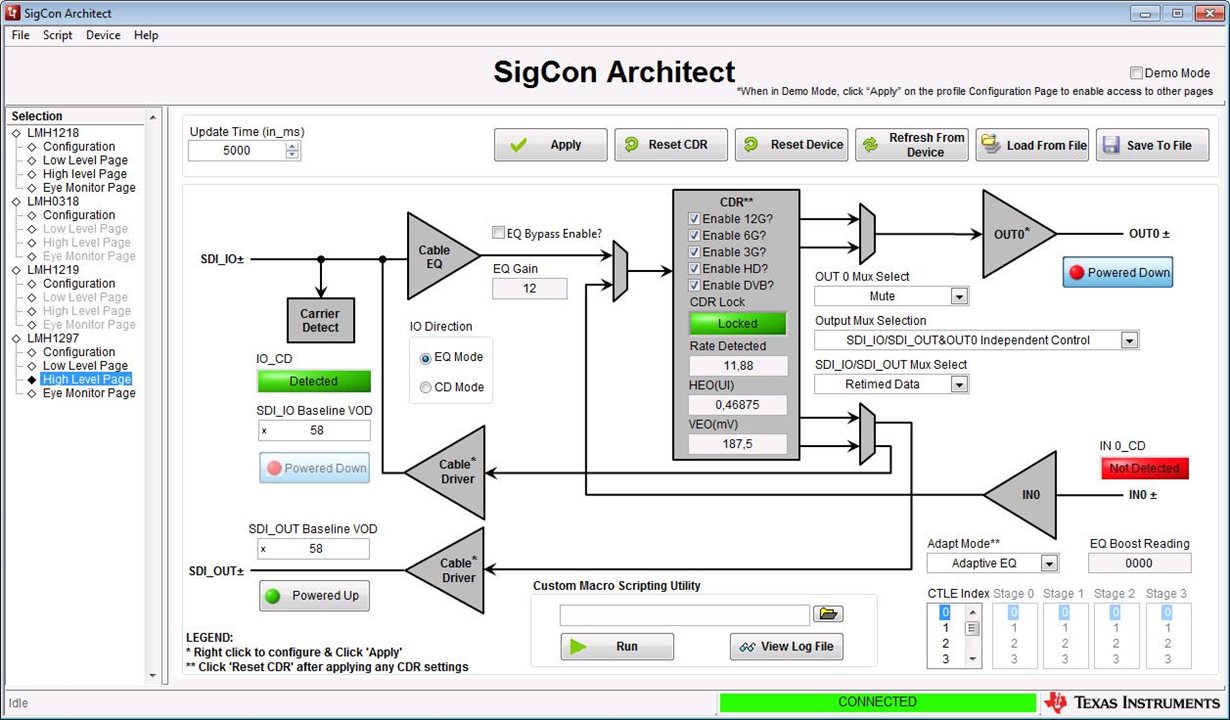

My customer is facing some errors and signal loss when 12G pathological signals are used with our LMH1297 (prototype board or EVM).

The signal is generated by a Phabrix QX. They use 1m cables from Belden (1694A) and HUBER+SUHNER Coaxial Cable Connector (11_BNC-75-5-20/133_N).

Below are his screen shots.

Would you have any idea where the issue comes from?

Regards,