Part Number: TSB43AB23

Hi Team,

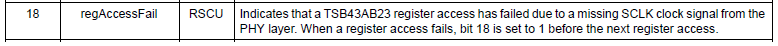

I would like to ask about Interrupt Event Register bit18 (regAccessFail).

Could you tell me how to handle (debug) when regAccessFail is set "1"?

I would also like to know if "SCLK clock signal from the PHY layer" is internal signal of TSB43AB23 or not.

The background of the question is my customer is facing the situation when accessing specific OHCI address.

Best Regards,

Yaita