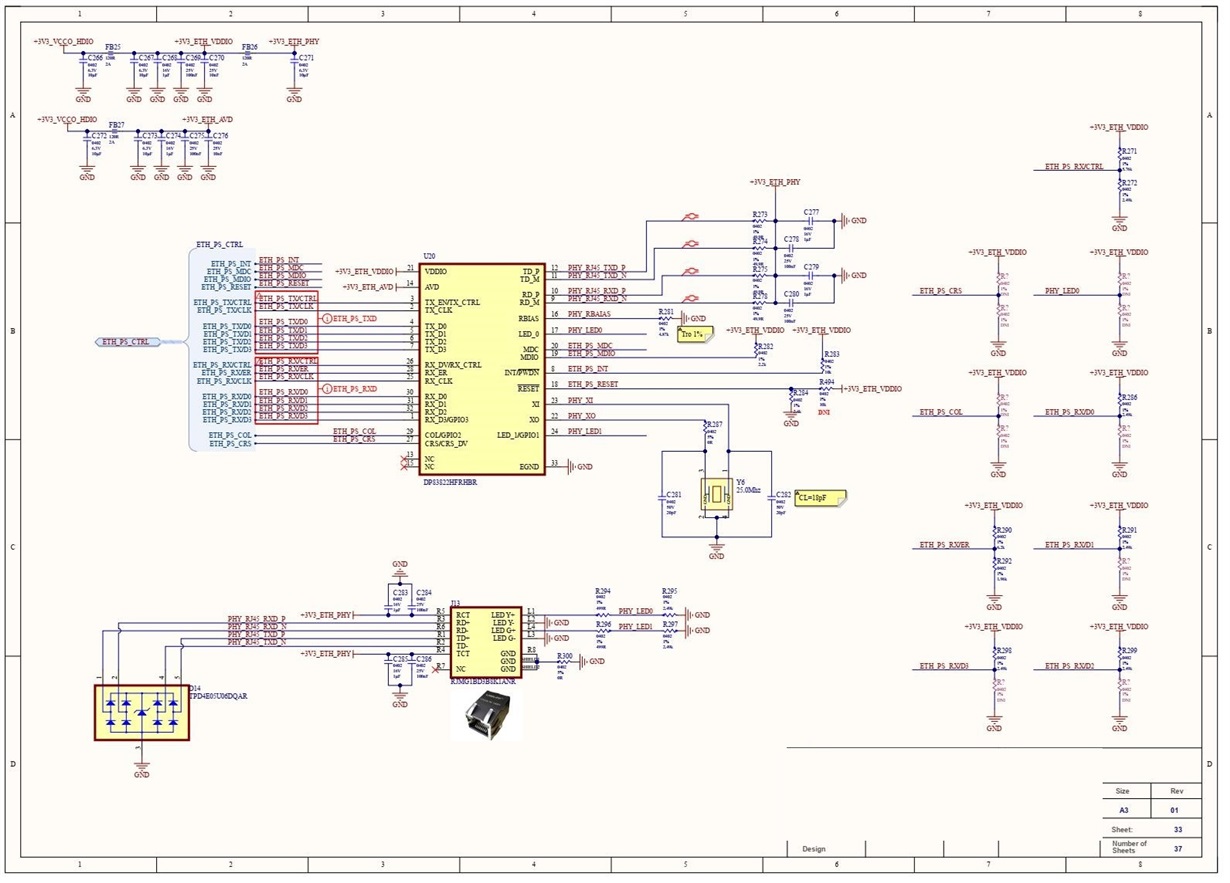

Part Number: DP83822HF

Hi team,

My customer is using DP83822HF in mode RGMII (100Mb, full duplex). They tried to config the PHY however they couldn't make it.

Auto-Negociation Complete - 0

Link-status - 0

I'd like to know what are the steps and register values to do that.