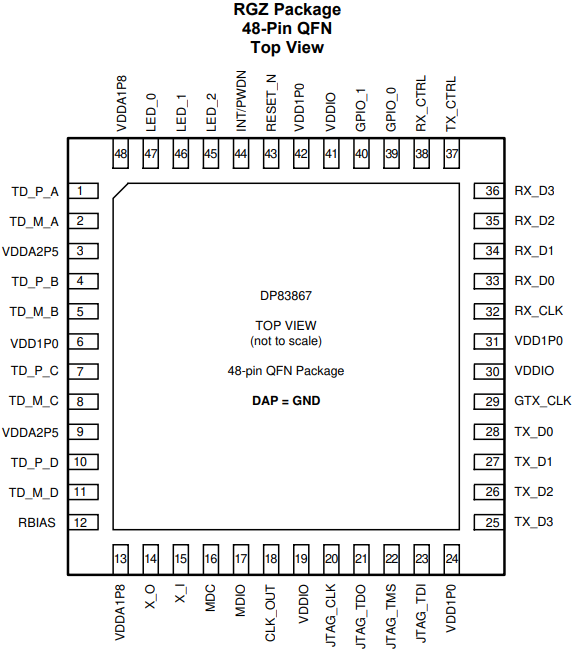

Part Number: DP83867ERGZ-S-EVM

Other Parts Discussed in Thread: USB-2-MDIO, DP83867E, DP83867IS, DP83867CS, DP83867CR, DP83867IR

Hello,

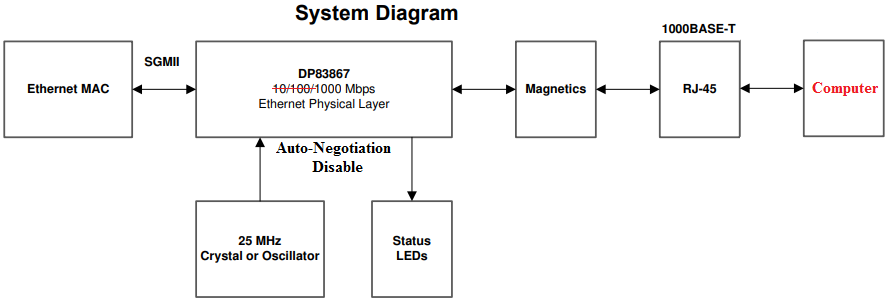

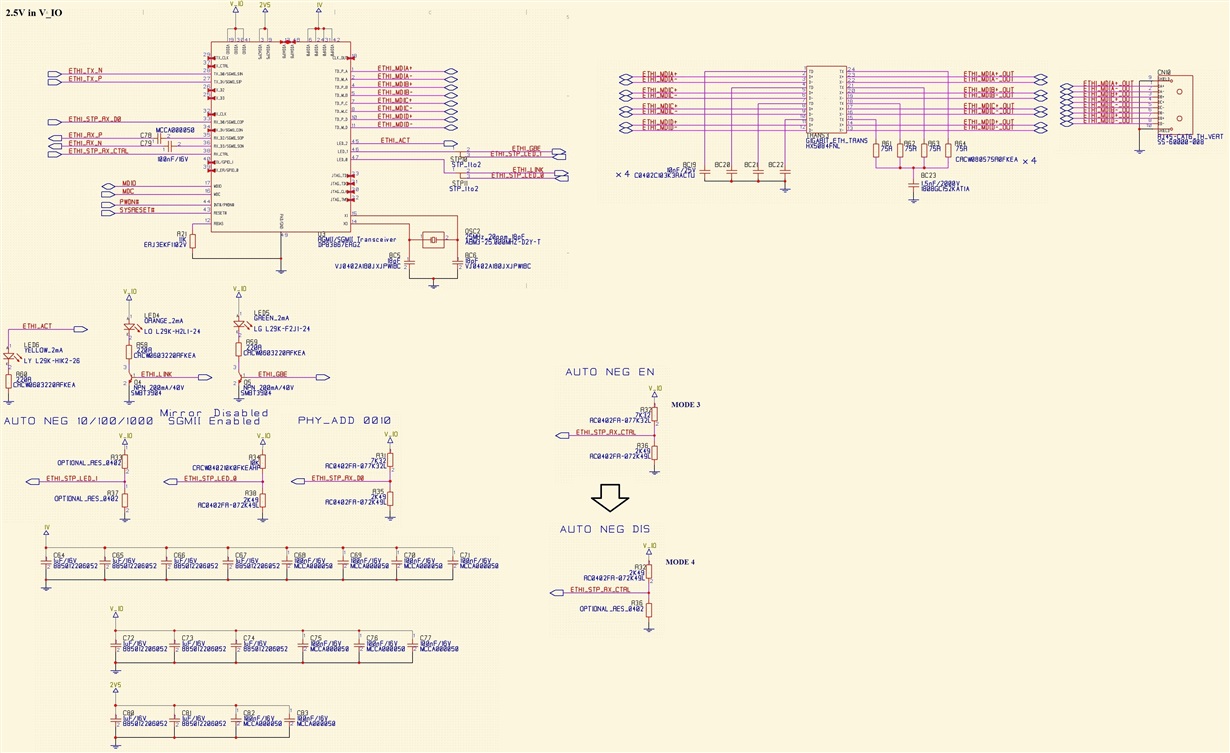

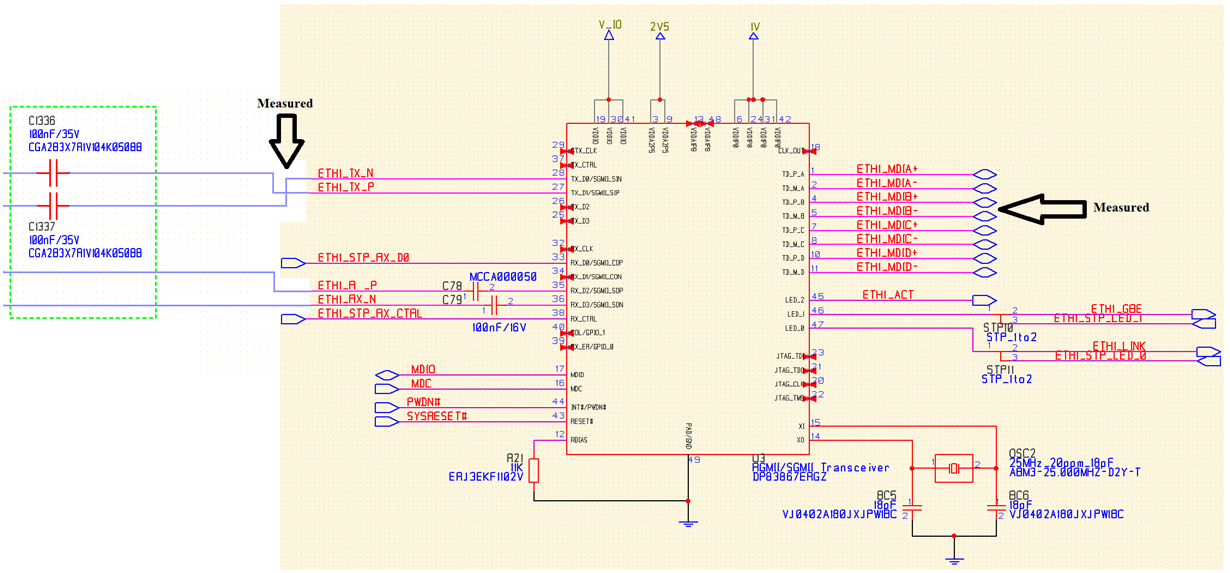

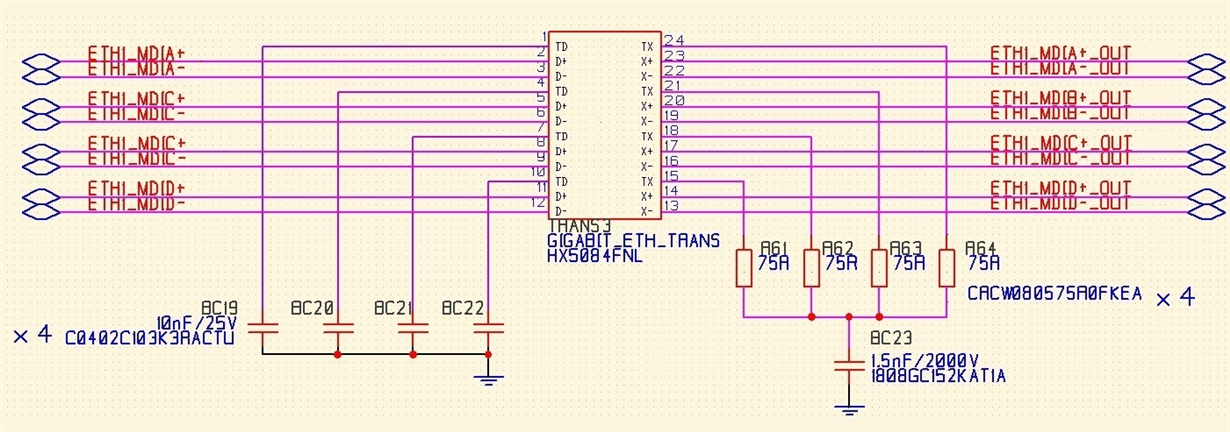

I would like to deactivate auto-negotiation using the "RX CTRL" pin of the DP83867ERGZ component.

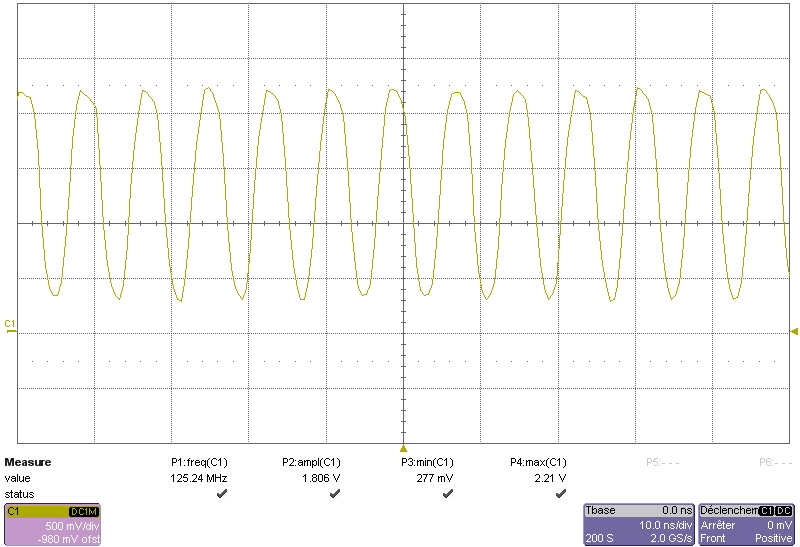

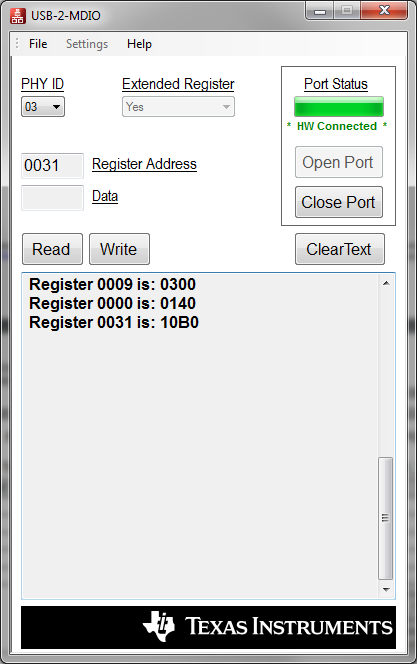

When I activate auto-negotiation by the "Rx_CTRL" in mode 3, the ethernet link is created with the computer

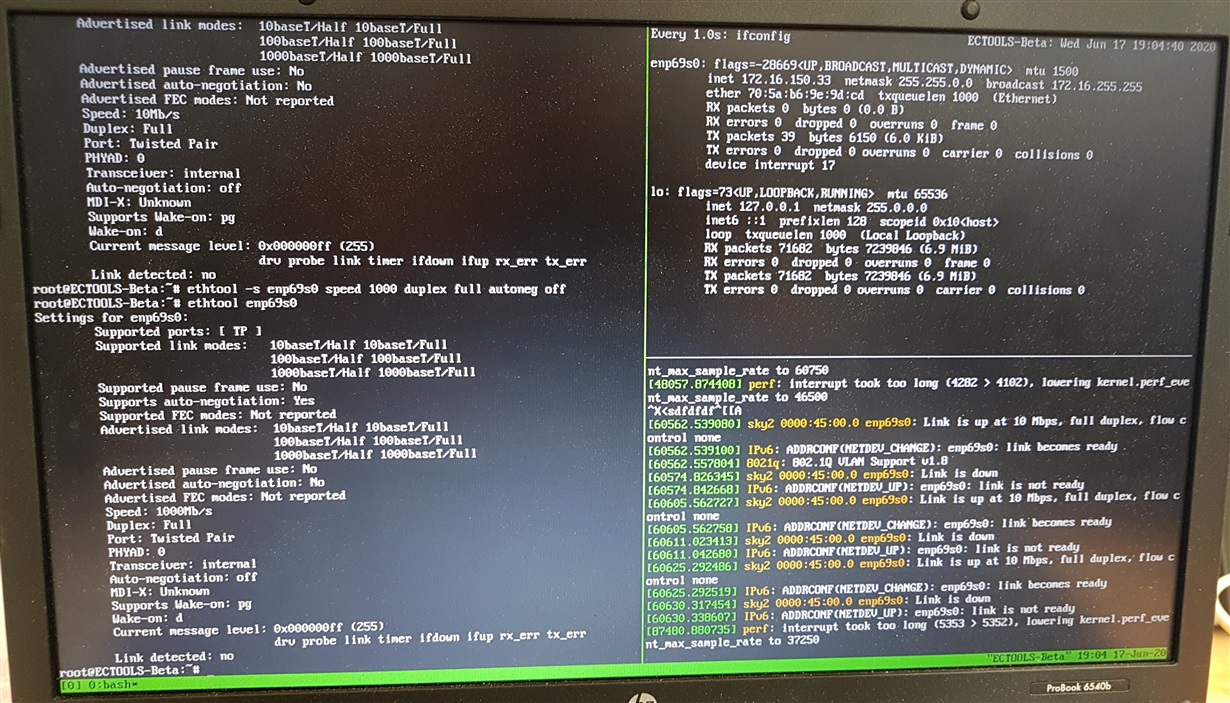

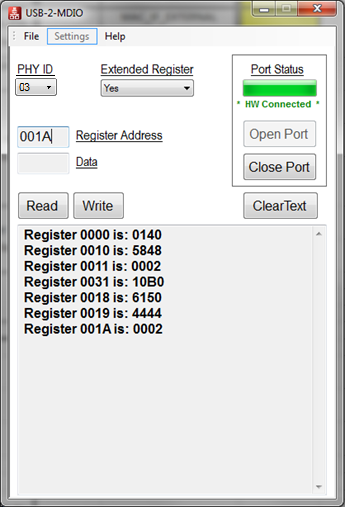

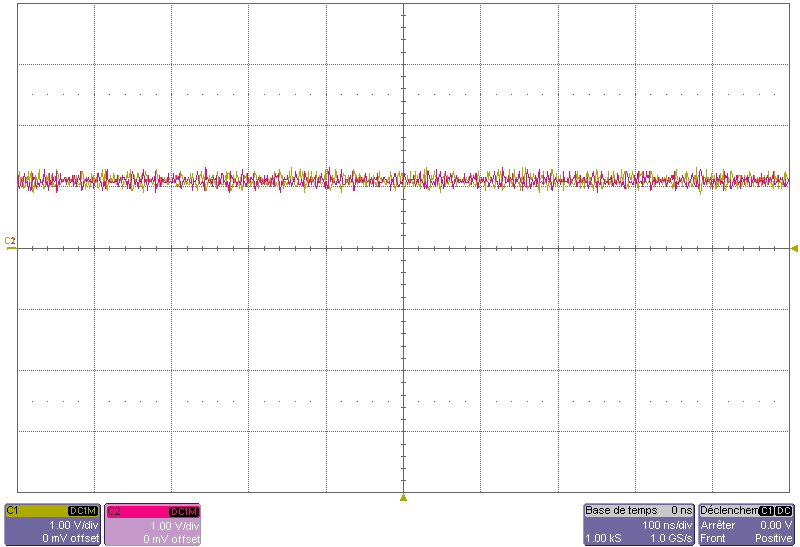

When I modify the "Rx_CTRL" pin in mode 4 to deactivate auto-negotiation. I cannot find an Ethernet link with a computer configured (see "Config computer" in attachment) :

bit 6 - SPEED SELECTION MSB Value by default -> 1, RW Comment -> Speed Select: See description for bit 13.

bit 12 and 4 are reserve