Hi Team,

My customer now use 947 and 948 to drive one display.

When enable 947 PATTERN MODE, the screen could display normally.

But when enable 948 PATTERN MODE, the screen could not display.

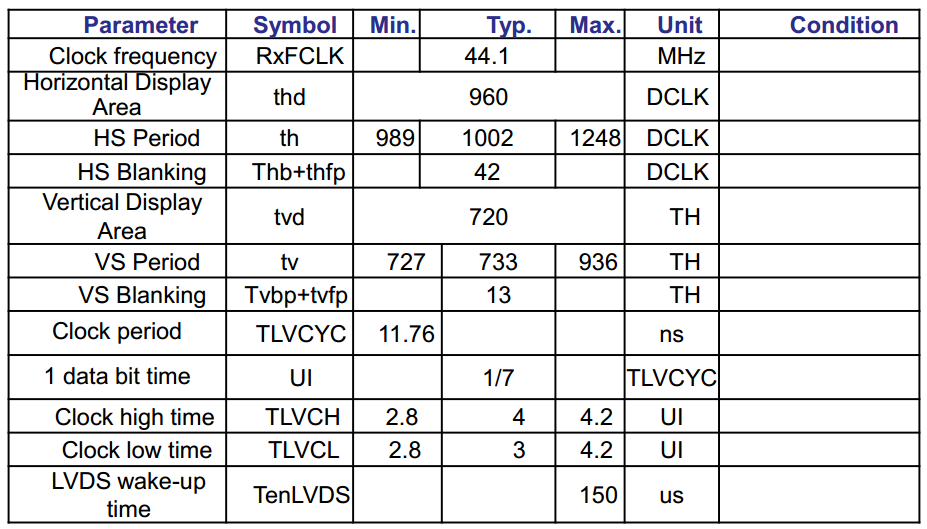

Here is the screen parameters.I found that the CLK only support 44.1MHz.

In 948, if divide radio is 2, this means 140MHz is 70MHz. And if use dual LVDS, the LVDS CLK is only 35MHz, which is much lower than the display clk requirement (44.1MHz).

I am not sure whether my analysis is correct. Could you please also tell me how to configure 948 PATTERN MODE to make it suitable for 44.1MHz?

Thanks!