Part Number: SN65HVD72

Hi,

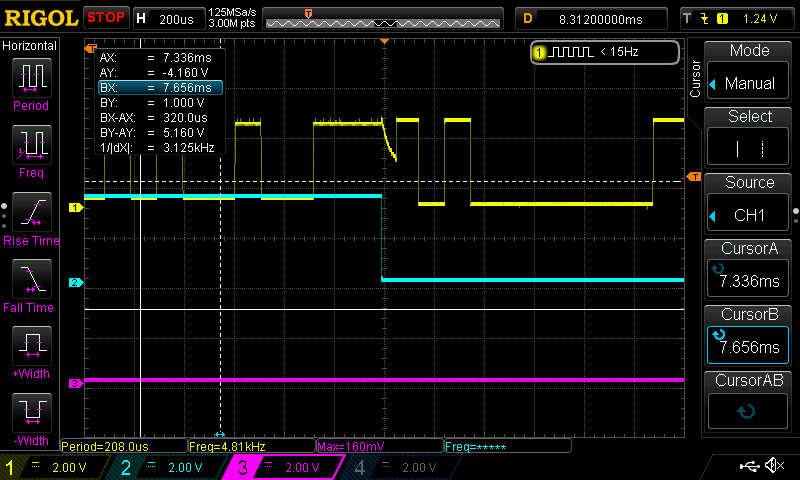

I'm using in my design mentioned RS485 transciever. I control RE, DE individually (not connected together or so). I measured with scope RX, TX lines from CPU to transciever + A,B lines and analyze data.

E.g. I'm sending those bytes (measured on CPU side):

sending 01 02 00 00 00 04 79 c9

and can see same on A/B signals (when translated)

But then I should receive:

received 01 02 01 01 60 48

And those bytes are available on A/B lines but then on RX side on CPU I got same buffer as sent: 01 02 00 00 00 04 79 c9 which puzzles me and I'm not sure what can cause that.

Any ideas what I can do wrong? I keep DE active in 1 only during transmission (during reception it's set to 0) and RE is still at 0.

Thanks.

marek