Dear support,

I am using two DP83825i phy with common SMI interface connected to an FPGA.

PHY1: address set to 0

PHY2: address set to 2

MDC clock frequency: ~100KHz

I am testing the SMI interface by reading the PHYIDR2 register.

From address 2, i got no answer. (the phy not even try to pull down the line)

From address 0, i got answer only every tenth attempt. I see no difference with oscilloscope in the signal integrity when i got answer or not.

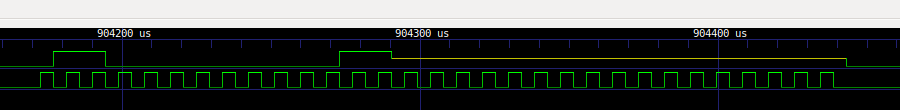

There is one of the simulation timing, measured on hardware as well:

If you have any suggestion to debug the problem I would be grateful.