Hi,

I would use SN75DPHY440SS, and I have two questions.

the conditions are 1600x1200 , 20fps , output format:YCbCr4:2:2, MIPI-CSI 2lane

Q1)

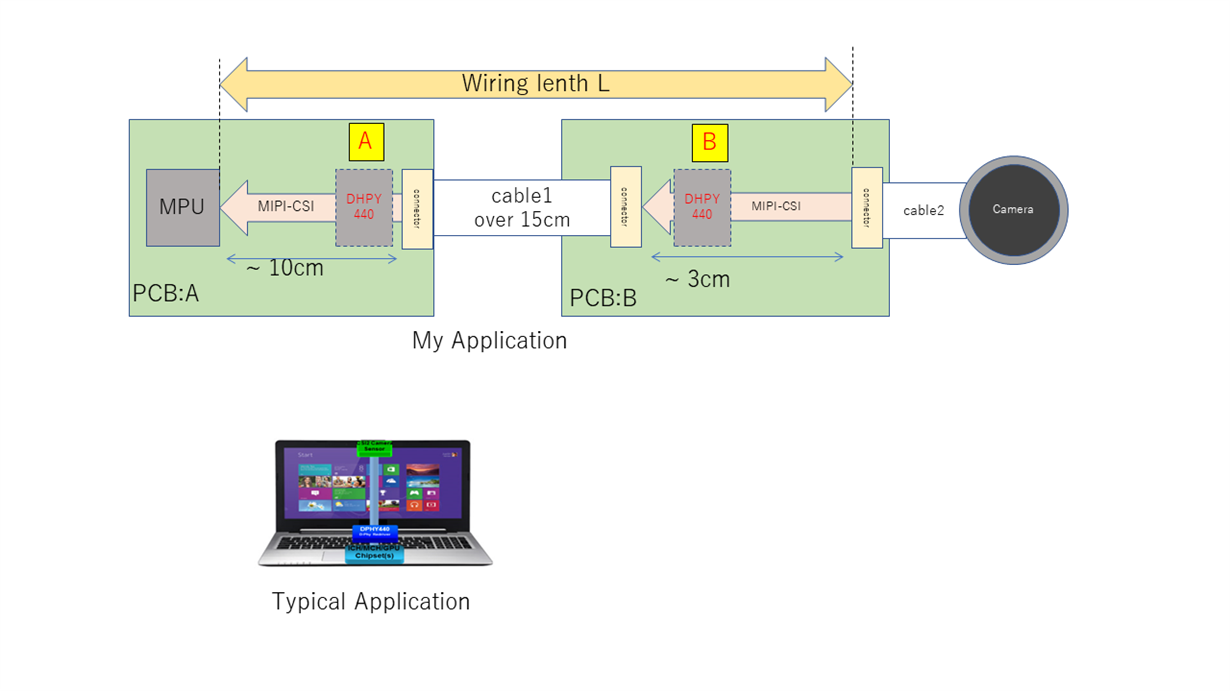

Is there a rule of thumb that the DPHY440 should be used when the length of the cable (1) or the wiring length L from the camera to the MPU is more than XXX centimeters?

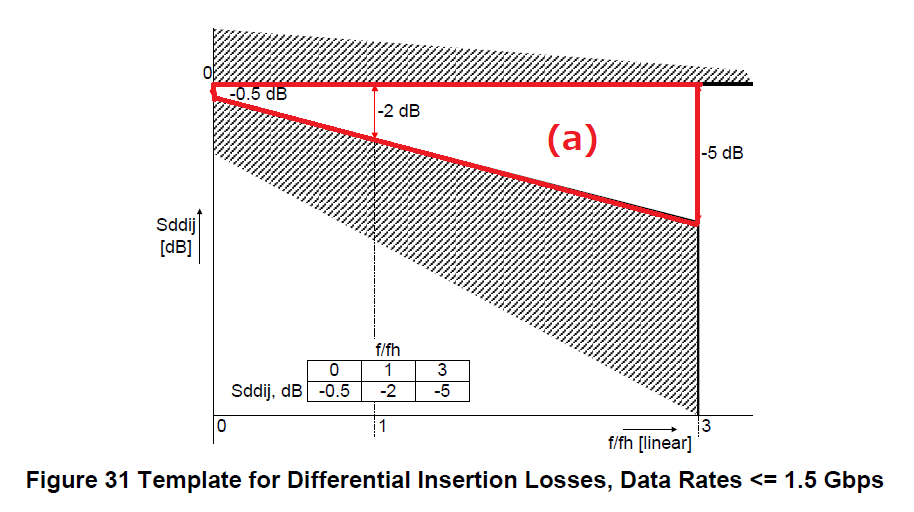

Or, with the resolution and frame rate of the camera used this time, the datarate is 307.2Mbps/lane, and it is not so high, so is there no necessity to use DPHY440?

Frequency calculation

the conditions are 1600x1200 2byte/pix 20fps

1600x1200x2x20x8=614.4Mbps

the num of data lane is 2

614.4Mpbs/2=307.2Mbps/lane

mipi clock is DDR

307.2/2=153.6MHz

Q2)

In the case of the configuration,My Application, which should be the mounting position of DPHY440, A position or B position?

Is it the position of A from the figure of "Typical Application" described in the data sheet sn75dphy440ss.pdf?