Part Number: DP83867IR

Hi colleague,

According to the comparison of GMII and MII:

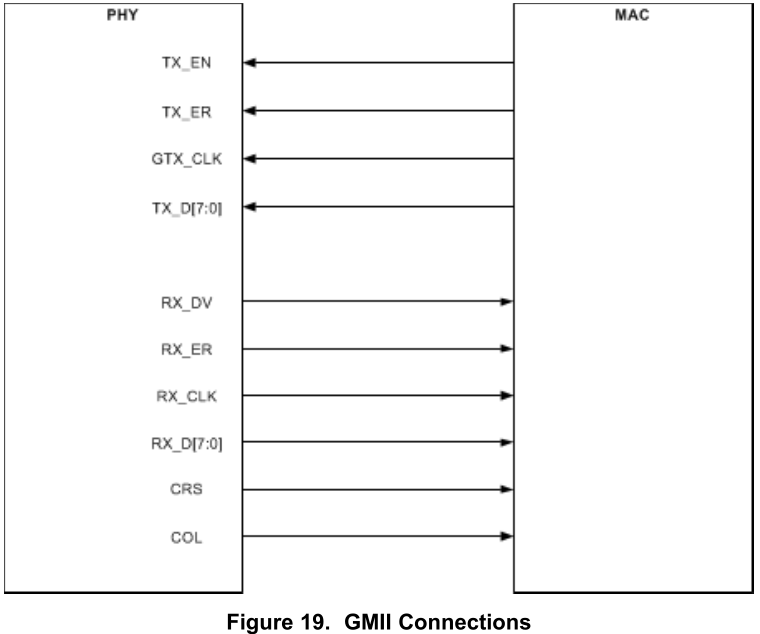

The difference between 1000M mode and 10M/100M mode is Tx_CLK use 25M (PHY output) or 125M (MAC output). But the GMII interface has only one TX_ CLK on the MAC side(FPGA) input pin. As shown in the figure below:

The customer wants to use GMII interface, therefore the customer idea is to read below register to adjust the current data rate, then configure the FPGA MAC clock.

They want to know whether this idea is right? If it is not right, how to realize 10/100/1000M self-adaption?

Thanks a lot!

Best Regards,

Rock Su