Other Parts Discussed in Thread: BQ25713, , BQ25703A, BQ25703

We have the TPS65987D mated with a BQ25713 such that the Type-C/PD port is both a [heavy up to 20V, 3A] sink and lightweight source (5V@1.5A) exploiting the BQ25713's bidirectional power capability. The TPS65987D has its GPIO1 connected to such BQ25713 pin.

We are wondering if TI has an actual application example of this being done (with the BQ25713 or any of its close BQ257xx relatives) and in particular what is the configuration done on the TPS65987D GPIO that drives such OtG pin.

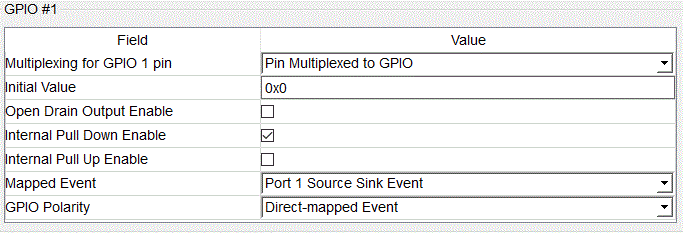

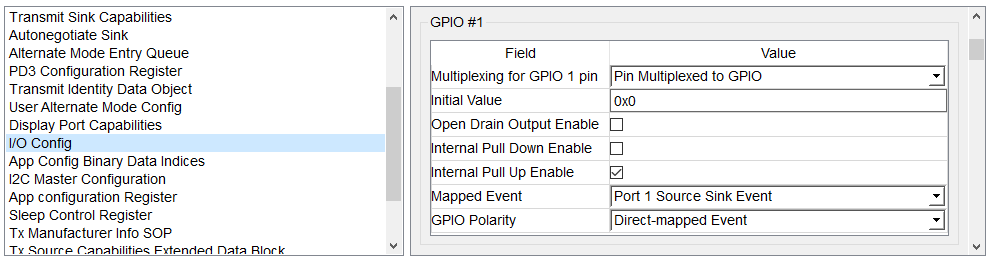

This is how we believe such GPIO1 ought to be configured:

This case is corollary to https://e2e.ti.com/support/interface/f/138/t/927370 (TPS65987D: Port 0 Source/Sink GPIO event unexpected behavior) where issues have been uncovered with such configuration and particularly when another port (GPIO20) is configured similarly but with opposite polarity for use in another circuit portion in our design.

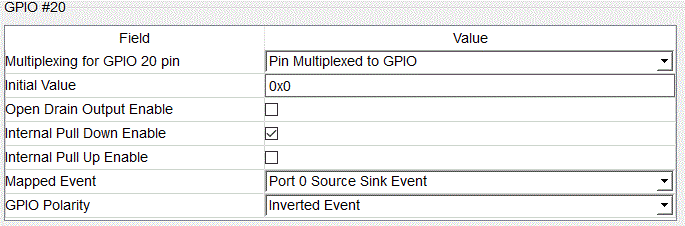

Such GPIO20 is configured as follows:

Thanks so much,

Georg A. Mussenden