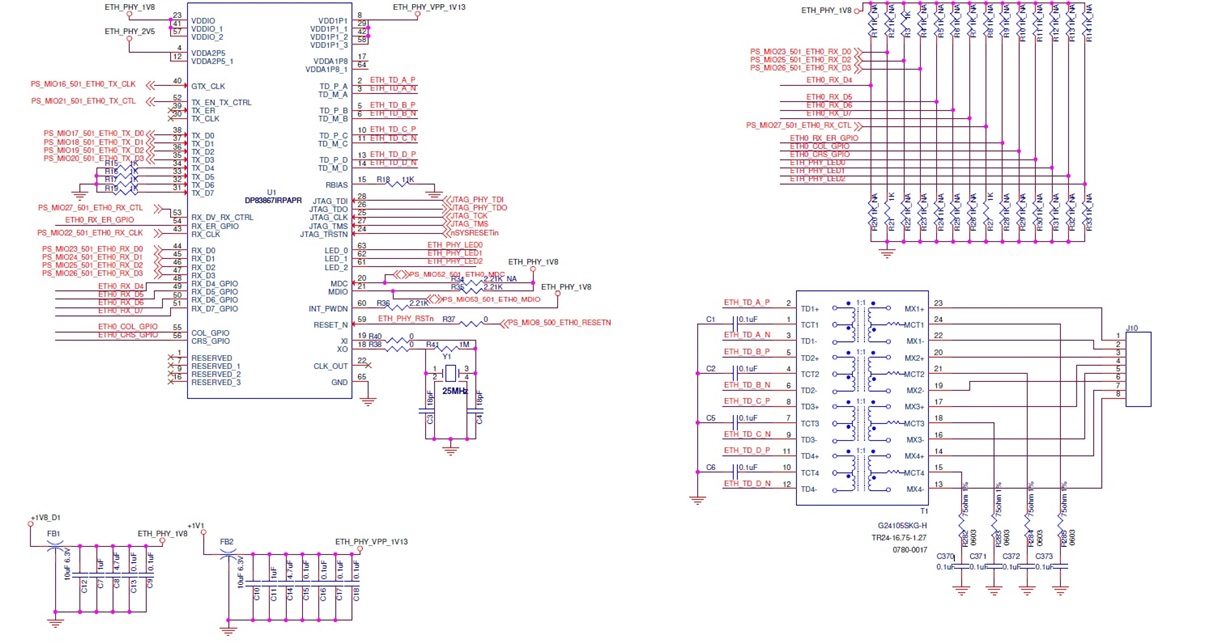

Part Number: DP83867IR

My design used zynq platform with DP83867.

It is not controlled MDIO on u-boot.

I find two cases.

Case 1: get the same date for every register address.

Case 2: get the 0x0000 data for every register address.

I try to check as below:

VDDIO ==> 1.8V

VDD1P1 ==> 1.1V

VDDA2P5 ==> 2.5V

RESET ==>1.8V

CLK_OUT ==>25MHz

RX_CLK ==> no signal

How to fix MDIO control issue?

My design as below

Capture MDIO waveform