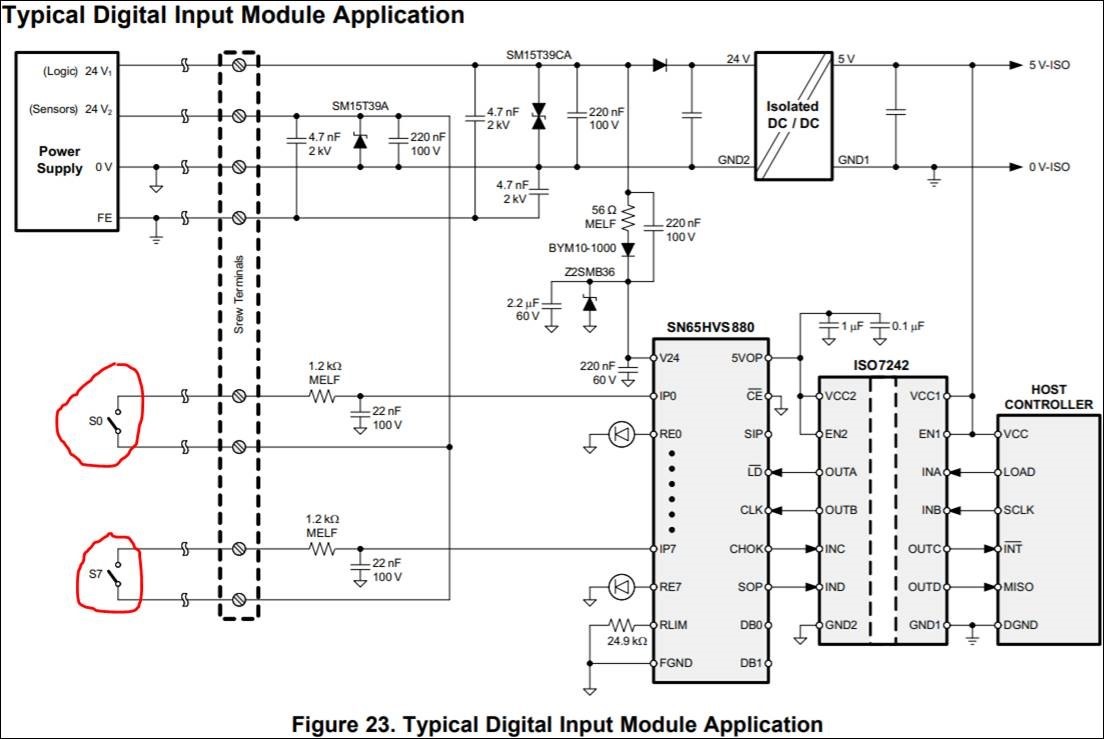

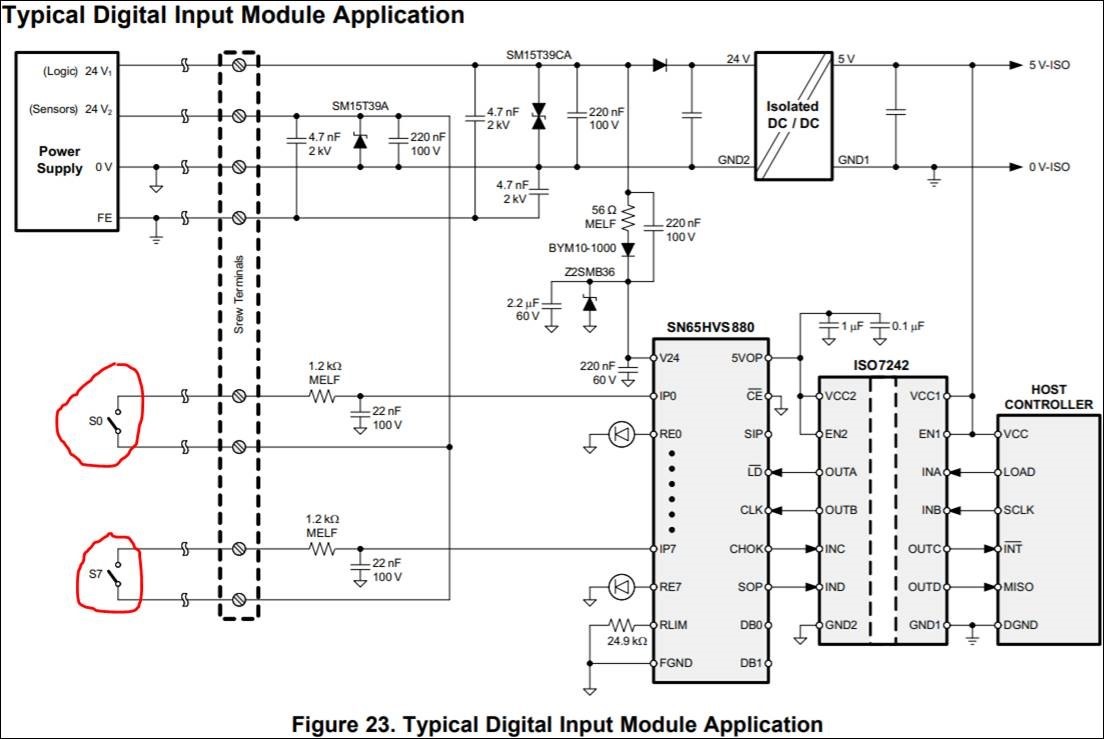

Part Number: SN65HVS880

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: SN65HVS880

Andrew,

I wouldn't quite call it high-z but it will register low. The default state of the input signals is low. Basically, when an input signal is applied there are multiple signal checks that the signal must go through to give a low-to-high transition of the input state.

Is the signal above 5.2V (High-level device input threshold voltage), is the input current higher than the leakage threshold (half the current limit set using the Rlim), and will this signal duration be longer than the debounce filter time (configured with DB0 and DB1)? The signal must pass all of these conditions before the serializer will register the input states as a high.

Hope this helps,

Rami Mooti