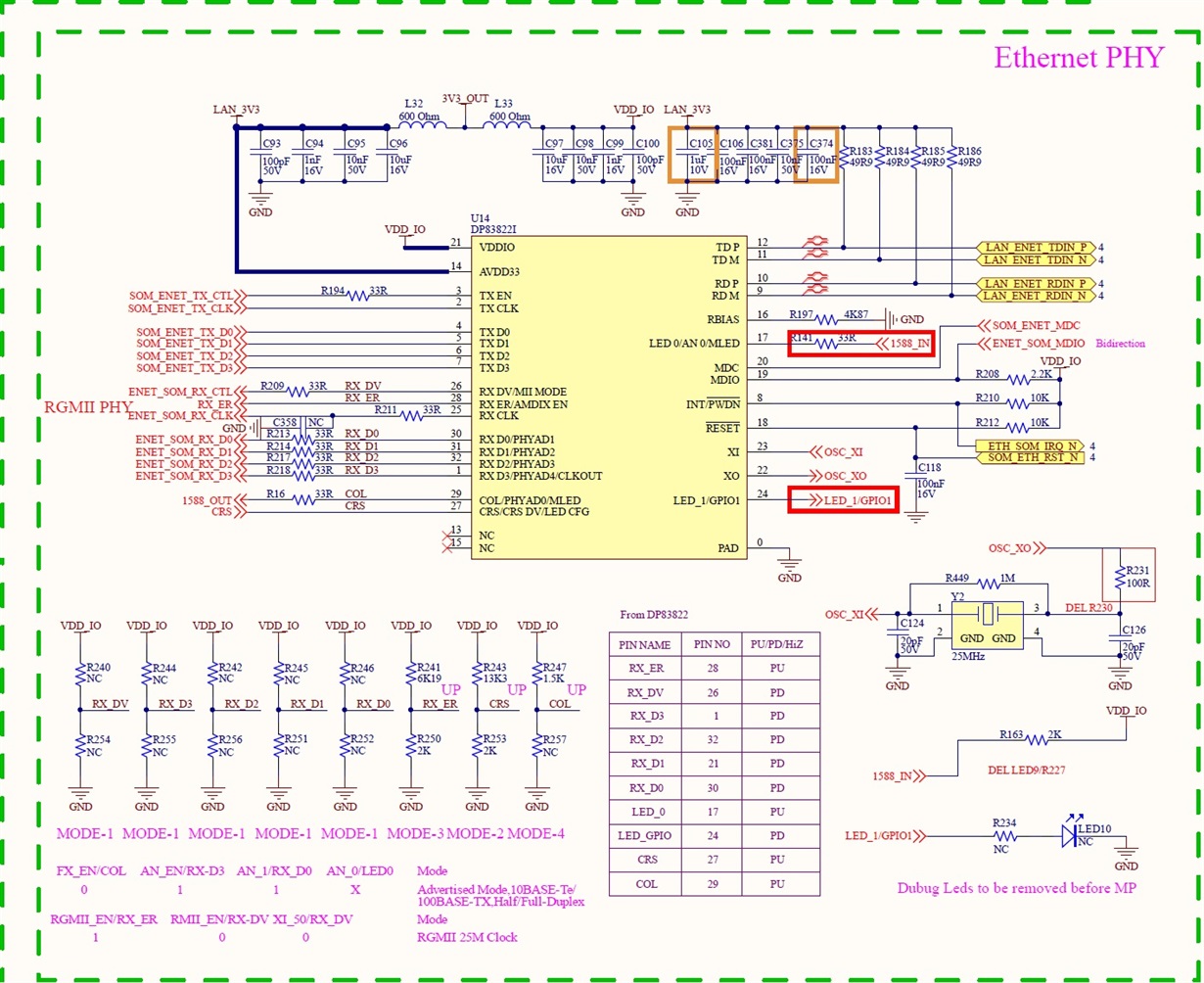

Part Number: DP83822I

Hi, Team

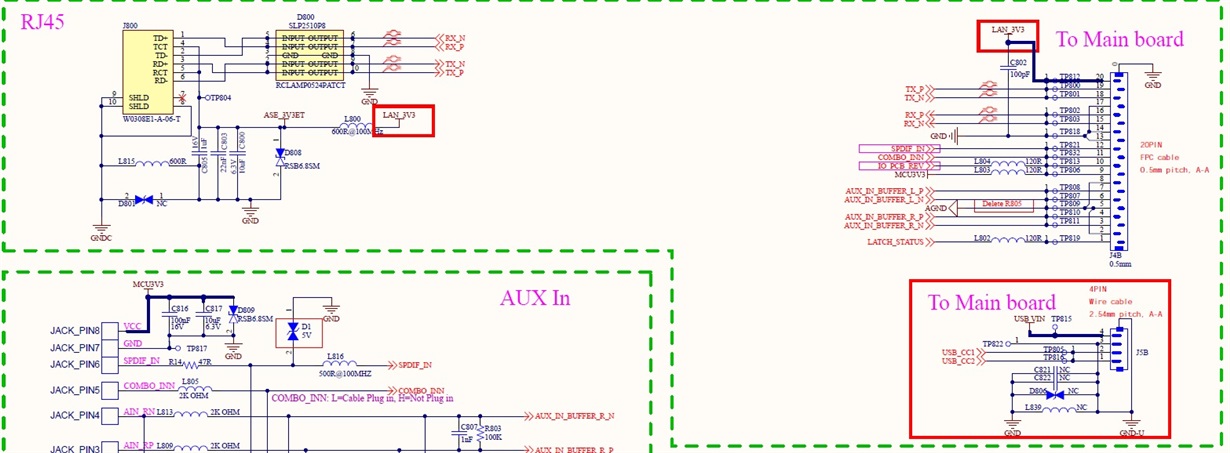

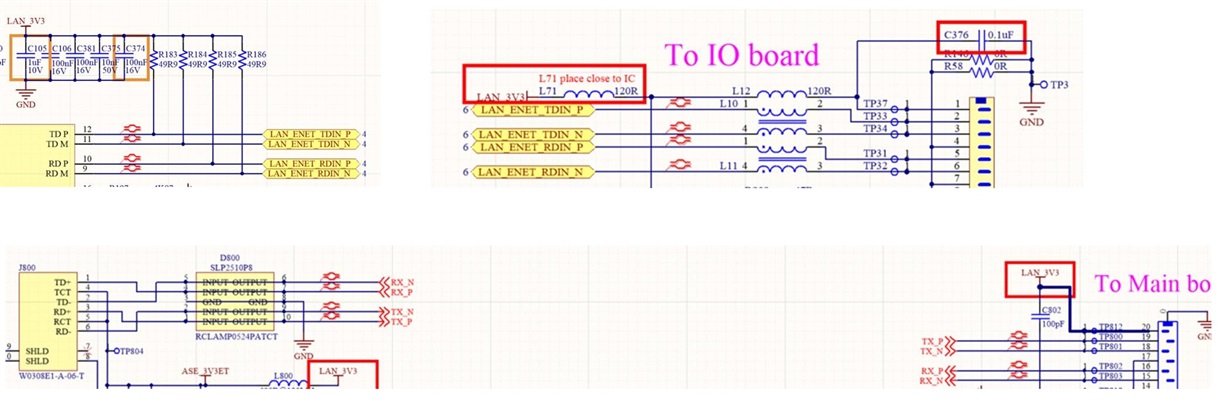

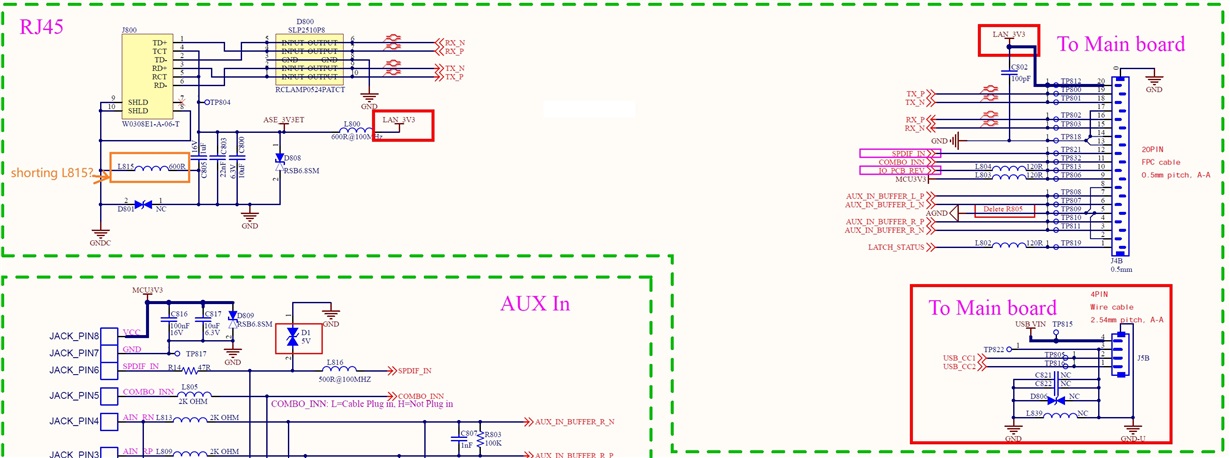

Our customer using DP83822I in the smart speaker, and they we meet the eye test failure( Twisted Pair Active Output Interface template).

Test report pls check the attach file.

Also, they using our DP83822I EVM connect to their MCU board, the eye test ( Twisted Pair Active Output Interface template) pass.

I am not sure whether it’s relate to any filter in the SCH.

Could u help to check and give some suggestions?

Thanks.

G.W