Other Parts Discussed in Thread: TCAN4550

Hiteam,

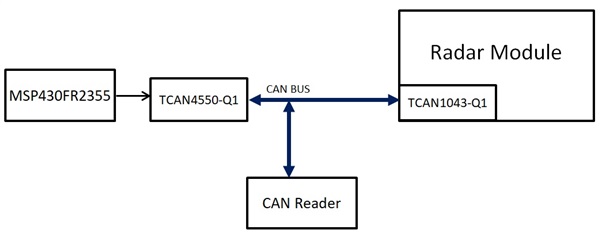

We are testing TCAN4550 in a car system. When the system power up, TCAN4550 ECU operates in the normal mode and keep sending data. At the same time when we hook up another CAN device(Radar module with CAN) on the bus, the TCAN4550 would stop working. And seems enter sleep mode.

Could you help to clarifym with the situation described above, what would happen on TCAN4550? And how we can do in system level to deal with this scenario and make TCAN4550 can resume

If we hook up the TCAN4550 ECU with radar module before system powering up, the interaction of TCAN4550 ECU and Radar module would function normally.

Regards,

Alex