Part Number: DP83867E

Hi Team,

A customer of mine is using the the DP83867ERGZT PHY for a project and needed some clarification on the SGMII mode implementation.

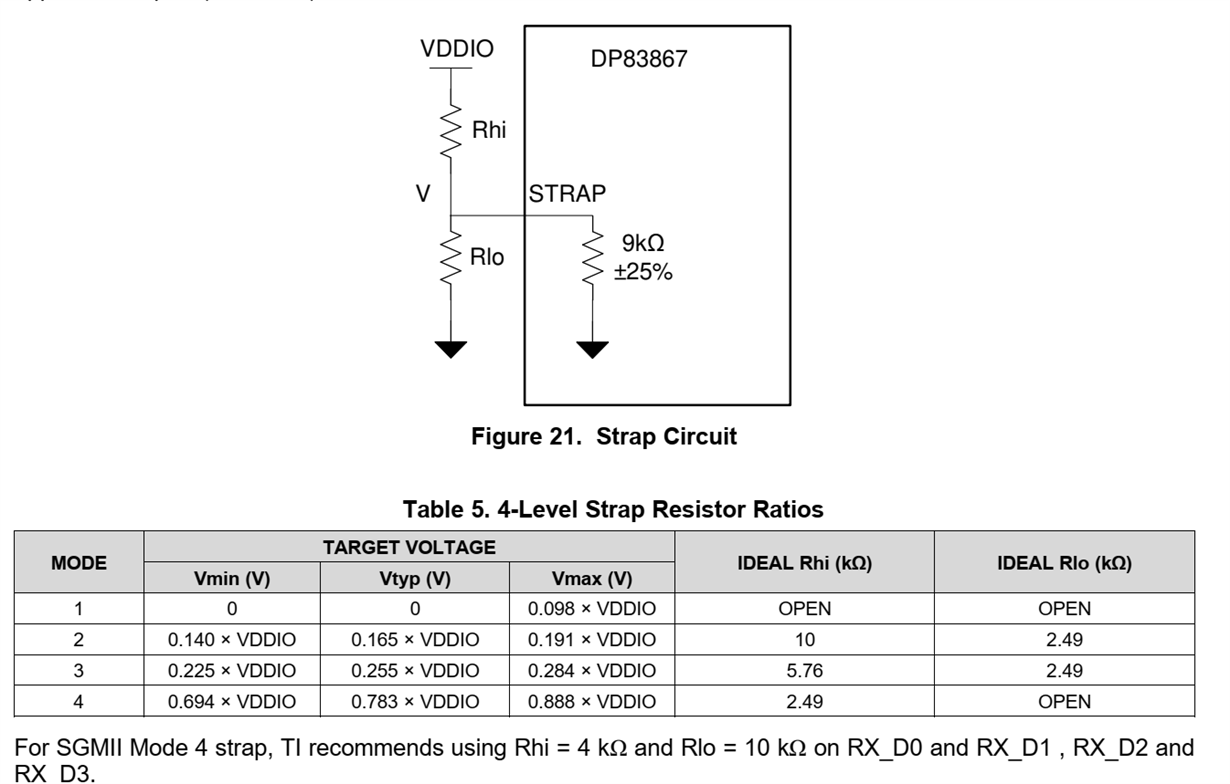

Currently they have implemented multiple PHY's in SGMII mode. Some of the PHY's are strapped with mode 4 on the RX_D0, RX_D1, RX_D2 and RX_D3 pins. According to the datasheet (page 37) this is done with Rhi=2k49 and Rlo=Open. Now there is also a note stating the following: "For SGMII Mode4 strap, TI recommends using Rhi = 4 kΩ and Rlo = 10 kΩ on RX_D0 and RX_D1, RX_D2 and RX_D3" (see the screenshot image below). They've tried, but can't seem to understand why this is recommended.

Could you elaborate on this? Does it not work when Rhi is set to 2k49 and Rlo is left open?

Thanks in advance for the support.

BR,

Obinna.