Hello

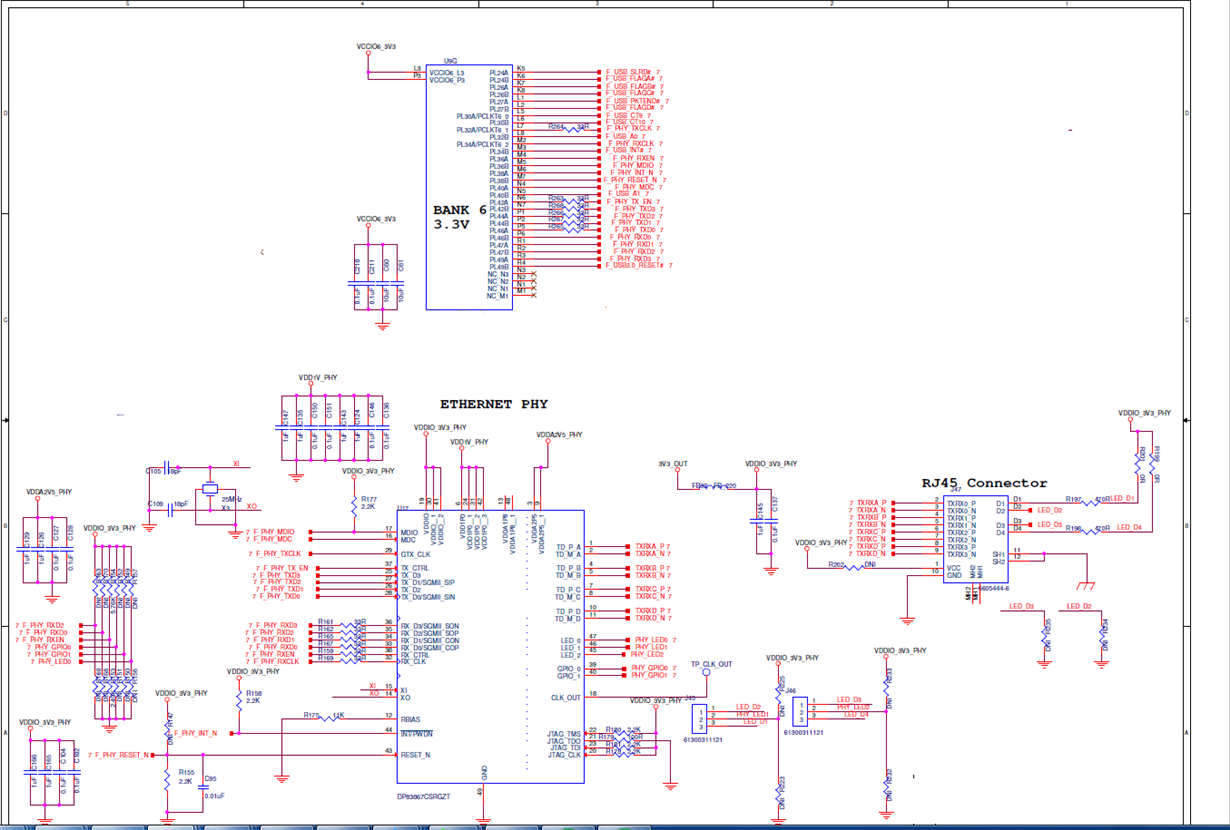

We are using DP83867CSRGZT in one of our designs and we are getting the same issue.

We are using the PHY in RGMII mode, and 10/100 Speed only.

The PHY is connected to FPGA and we are using External Ethernet Analyzer to send and receive data, but we are getting FCS errors) in the Analyser. ( (we tried shifted RX and TX clock in all possible ways)

Also, we tried to check the issue using the DP83867 Troubleshooting Guide and the below points are checked and found OK.

1. Power supplies are fine

2. RBIAS Voltage and resistance is fine

3. Reset and clock are also fine

4. We are able to read and write on MDIO.

5. Reverse loopback is working fine but MII loopback is not working fine(We are not getting correct data in FPGA)

PFA Schematic for your reference, Can you please verify once and let us know how this can be resolved.

Regards

Akash